## USING VISUALIZATION TO UNDERSTAND THE BEHAVIOR OF COMPUTER SYSTEMS

# A DISSERTATION SUBMITTED TO THE DEPARTMENT OF COMPUTER SCIENCE AND THE COMMITTEE ON GRADUATE STUDIES OF STANFORD UNIVERSITY IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

Robert P. Bosch Jr. August 2001

© Copyright by Robert P. Bosch Jr. 2001 All Rights Reserved

| I certify that I have read this dissertation and and quality, as a dissertation for the degree | I that in my opinion it is fully adequate, in scope of Doctor of Philosophy. |

|------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

|                                                                                                | Dr. Mendel Rosenblum<br>(Principal Advisor)                                  |

|                                                                                                |                                                                              |

| I certify that I have read this dissertation and and quality, as a dissertation for the degree | I that in my opinion it is fully adequate, in scope of Doctor of Philosophy. |

| _                                                                                              | Dr. Pat Hanrahan                                                             |

|                                                                                                |                                                                              |

| I certify that I have read this dissertation and and quality, as a dissertation for the degree | I that in my opinion it is fully adequate, in scope of Doctor of Philosophy. |

|                                                                                                | Dr. Mark Horowitz                                                            |

|                                                                                                |                                                                              |

| Approved for the University Committee on                                                       | Graduate Studies:                                                            |

|                                                                                                |                                                                              |

### **Abstract**

As computer systems continue to grow rapidly in both complexity and scale, developers need tools to help them understand the behavior and performance of these systems. While information visualization is a promising technique, most existing computer systems visualizations have focused on very specific problems and data sources, limiting their applicability.

This dissertation introduces Rivet, a general-purpose environment for the development of computer systems visualizations. Rivet can be used for both real-time and post-mortem analyses of data from a wide variety of sources. The modular architecture of Rivet enables sophisticated visualizations to be assembled using simple building blocks representing the data, the visual representations, and the mappings between them. The implementation of Rivet enables the rapid prototyping of visualizations through a scripting language interface while still providing high-performance graphics and data management.

The effectiveness of Rivet as a tool for computer systems analysis is demonstrated through a collection of case studies. Visualizations created using Rivet have been used to display: (a) line-by-line execution data from the SUIF Explorer interactive parallelizing compiler, enabling programmers to maximize the parallel speedups of their applications; (b) detailed memory system utilization data from the FlashPoint memory profiler, providing insights on both sequential and parallel program bottlenecks; (c) the behavior of applications running on superscalar processors, allowing developers to take full advantage of these complex CPUs; and (d) the real-time performance of computer systems and clusters, drawing attention to interesting or anomalous behavior.

In addition to these focused examples, Rivet has been also used in conjunction with more comprehensive data sources such as the SimOS complete machine simulator. A detailed performance analysis of the Argus parallel graphics library demonstrates how these tools combine to provide a powerful iterative analysis framework for understanding computer systems as a whole.

## **Acknowledgments**

There are many people I would like to thank for making this dissertation possible, and for making my stay at Stanford so enjoyable that I decided to stick around for eight years.

My advisor, Mendel Rosenblum, has been an incredibly patient mentor and good friend throughout my time at Stanford. He taught me how to perform computer systems research, and how to design, implement, and debug large software systems. Any failings on either score are strictly the fault of the student, not the teacher.

Pat Hanrahan, co-founder with Mendel of the Rivet project, took a color-blind systems student with no background in computer graphics, and instilled in me a love and appreciation of both the history and the potential power and richness of information visualization.

Mark Horowitz served on both my orals committee and my reading committee; his comments and suggestions significantly improved the quality of this dissertation.

My officemates and partners-in-crime in the Rivet group, Chris Stolte and Diane Tang, made me look forward to coming to the office every day. Working with them greatly improved my own productivity, not to mention my state of mind. I will always fondly remember the late-night hacking sessions, the paper-writing deadline crunches, the shouting matches at the whiteboard, and the football-tossing sessions that made Studio 354 such a wonderful place to work.

John Gerth contributed to the design of Rivet from the very first days of the project through its many incarnations as it evolved over the years. He was also a great source of stories, insights, and wisdom about visualization, computer science, baseball, and life.

One of the best aspects of working on this research was the opportunity to collaborate with so many talented and good people from groups throughout the computer systems laboratory. The case studies presented here benefited from the significant contributions of Shih-Wei Liao (SUIF Explorer), Jeff Gibson (Thor), Donald Knuth (PipeCleaner), John Gerth (Visible Computer), and Gordon Stoll (Argus).

Before getting started on the Rivet project, I worked on SimOS in the Hive research group, part of the larger FLASH multiprocessor project. The Hive and FLASH folks really helped me jump-start my academic career, giving me valuable hacking experience and many great friendships.

In particular, my original officemates in Gates, Steve Herrod and John Heinlein, pulled me out of my shell and helped me get more closely integrated into the group both academically and socially, which made a huge difference to both my research and my overall enjoyment of graduate school.

The systems support staff — John Gerth, Charlie Orgish, Thoi Nguyen, and Kevin Colton — worked long and hard to keep the computer systems up and running smoothly, and the administrative staff — Ada Glucksman, Heather Gentner, and Chris Lilly — did an equally fine job dealing with the bureaucratic aspects of life at Stanford. Their work made my life at Stanford much easier and is greatly appreciated.

This research was supported by several funding sources: the Office of Naval Research through its graduate fellowship program, DARPA through contract DABT63-94-C-0054, and the Department of Energy through its ASCI Level One Alliance with Stanford University. I hope they consider it money well-spent; I know I sure do.

Finally, I would like to thank my family for their enduring love and support. My parents, Bob and Georgi, worked and sacrificed to give me every opportunity to succeed in life. I know they often suspected that I would stay in school forever, and understandably so; hopefully, however, the completion of this dissertation finally convinces them otherwise. And while the transition from academia to the Real World will no doubt be difficult, I look forward to facing the challenges together with the love of my life, my wife Ming. I cannot imagine how I could have gotten through graduate school without her by my side.

## **Contents**

| Al | Abstract |         |                                             |    |  |  |

|----|----------|---------|---------------------------------------------|----|--|--|

| A  | cknow    | ledgme  | ents                                        | v  |  |  |

| 1  | Intr     | oductio | n                                           | 1  |  |  |

|    | 1.1      | The ch  | nallenge: understanding complex systems     | 1  |  |  |

|    | 1.2      | The R   | ivet approach: interactive data exploration | 2  |  |  |

|    | 1.3      | Organi  | ization of this dissertation                | 4  |  |  |

| 2  | The      | Rivet V | isualization Environment                    | 6  |  |  |

|    | 2.1      | Archit  | ecture                                      | 7  |  |  |

|    |          | 2.1.1   | Data management                             | 7  |  |  |

|    |          | 2.1.2   | Visual representation                       | 10 |  |  |

|    |          | 2.1.3   | Display resource management                 | 12 |  |  |

|    |          | 2.1.4   | Coordination                                | 13 |  |  |

|    |          | 2.1.5   | Architecture discussion                     | 16 |  |  |

|    | 2.2      | Imple   | mentation                                   | 17 |  |  |

|    |          | 2.2.1   | Performance                                 | 17 |  |  |

|    |          | 2.2.2   | Flexibility                                 | 18 |  |  |

|    | 2.3      | Summ    | ary                                         | 18 |  |  |

| 3  | Inte     | ractive | Parallelization: SUIF Explorer              | 19 |  |  |

|    | 3.1      | Backg   | round                                       | 19 |  |  |

|    | 3.2      | Visual  | ization                                     | 20 |  |  |

|    |          | 3.2.1   | Overview                                    | 22 |  |  |

|    |          | 3.2.2   | Source view                                 | 22 |  |  |

|    |          | 3.2.3   | Controls                                    | 22 |  |  |

|                | 3.3  | Rivet features                            | 23 |  |  |

|----------------|------|-------------------------------------------|----|--|--|

|                | 3.4  | Examples                                  | 23 |  |  |

|                |      | 3.4.1 MDG                                 | 25 |  |  |

|                |      | 3.4.2 Applu                               | 25 |  |  |

|                | 3.5  | Discussion                                | 27 |  |  |

| 4              | Men  | nory Profiling: Thor                      | 28 |  |  |

|                | 4.1  | Background                                | 28 |  |  |

|                | 4.2  | Visualization                             | 29 |  |  |

|                | 4.3  | Rivet features                            | 31 |  |  |

|                | 4.4  | Examples                                  | 31 |  |  |

|                |      | 4.4.1 FFT                                 | 31 |  |  |

|                |      | 4.4.2 LU                                  | 33 |  |  |

|                | 4.5  | Discussion                                | 35 |  |  |

| 5              | Sup  | erscalar Processors: PipeCleaner          | 36 |  |  |

|                | 5.1  | Background                                | 36 |  |  |

|                | 5.2  | Related work                              | 39 |  |  |

|                | 5.3  | Visualization                             | 40 |  |  |

|                |      | 5.3.1 Timeline view: Finding problems     | 40 |  |  |

|                |      | 5.3.2 Pipeline view: Identifying problems | 42 |  |  |

|                |      | 5.3.3 Source code view: Providing context | 45 |  |  |

|                | 5.4  | Rivet features                            | 45 |  |  |

|                | 5.5  | Examples                                  | 46 |  |  |

|                |      | 5.5.1 Program development                 | 47 |  |  |

|                |      | 5.5.2 Hardware design                     | 48 |  |  |

|                | 5.6  | Other applications                        | 49 |  |  |

|                |      | 5.6.1 Compiler design                     | 49 |  |  |

|                |      | 5.6.2 Simulator development               | 50 |  |  |

|                |      | 5.6.3 Other problem domains               | 50 |  |  |

| 6              | Real | l-time Monitoring: The Visible Computer   | 52 |  |  |

| 6.1 Background |      |                                           |    |  |  |

|                | 6.2  | Visualization                             | 53 |  |  |

|                |      | 6.2.1 Layout                              | 53 |  |  |

|                |      | 6.2.2 Data display                        | 56 |  |  |

|    | 6.3    | Rivet features                               | 57        |

|----|--------|----------------------------------------------|-----------|

|    | 6.4    | Example: Database client/server application  | 58        |

|    |        | 6.4.1 Cycle 21 million                       | 58        |

|    |        | 6.4.2 Cycle 63 million                       | 58        |

|    |        | 6.4.3 Cycle 126 million                      | 60        |

|    | 6.5    | Discussion                                   | 60        |

| 7  | Ad l   | hoc Visualization and Analysis               | 61        |

|    | 7.1    | Background                                   | 62        |

|    | 7.2    | Related work                                 | 63        |

|    | 7.3    | Argus performance analysis                   | 64        |

|    |        | 7.3.1 Argus background                       | 64        |

|    |        | 7.3.2 Simulation environment                 | 65        |

|    |        | 7.3.3 Memory system analysis                 | 66        |

|    |        | 7.3.4 Process scheduling analysis            | 68        |

|    |        | 7.3.5 Preventing process migration           | 73        |

|    |        | 7.3.6 Changing the multiprocessing mechanism | 75        |

|    | 7.4    | Discussion                                   | 75        |

| 8  | Disc   | eussion                                      | <b>78</b> |

|    | 8.1    | Rapid prototyping                            | 78        |

|    | 8.2    | Modular architecture                         | 80        |

|    | 8.3    | Integrating analysis and visualization       | 81        |

|    | 8.4    | Summary                                      | 82        |

| Bi | bliogi | raphy                                        | 85        |

## **List of Tables**

| 3.1 | Sample output produced by SUIF Explorer's dynamic analysis tools | 20 |

|-----|------------------------------------------------------------------|----|

| 8.1 | Visualization script lengths                                     | 79 |

## **List of Figures**

| 2.1 | Schematic depiction of information flow in Rivet           | 7  |

|-----|------------------------------------------------------------|----|

| 2.2 | Schematics of Rivet data objects                           | 8  |

| 2.3 | Rivet Metaphor schematic                                   | 11 |

| 2.4 | Rivet Primitive schematic                                  | 12 |

| 2.5 | Example of a coordinated multi-view visualization in Rivet | 15 |

| 3.1 | SUIF Explorer visualization                                | 21 |

| 3.2 | SUIF Explorer visualization of MDG                         | 24 |

| 3.3 | SUIF Explorer visualization of Applu                       | 26 |

| 4.1 | Thor visualization                                         | 30 |

| 4.2 | Thor visualizations of FFT                                 | 32 |

| 4.3 | Thor visualizations of LU                                  | 34 |

| 5.1 | PipeCleaner timeline view                                  | 41 |

| 5.2 | PipeCleaner animated pipeline view                         | 42 |

| 5.3 | Examples of pipeline hazards                               | 44 |

| 5.4 | PipeCleaner source code view                               | 45 |

| 5.5 | Complete PipeCleaner visualization                         | 47 |

| 5.6 | MMIX pipeline visualization                                | 49 |

| 6.1 | Hardware hierarchy of a workstation cluster                | 53 |

| 6.2 | Visible Computer: Nested hierarchy layout                  | 54 |

| 6.3 | Visible Computer: Grouping and ungrouping of instances     | 55 |

| 6.4 | Visible Computer: Strip charts and active icons            | 56 |

| 6.5 | Visible Computer analysis of a database running on SimOS   | 59 |

| 7.1 | Initial speedup curve for Argus on SimOS                   | 66 |

| 7.2 | MView visualization of Argus                               | 67 |

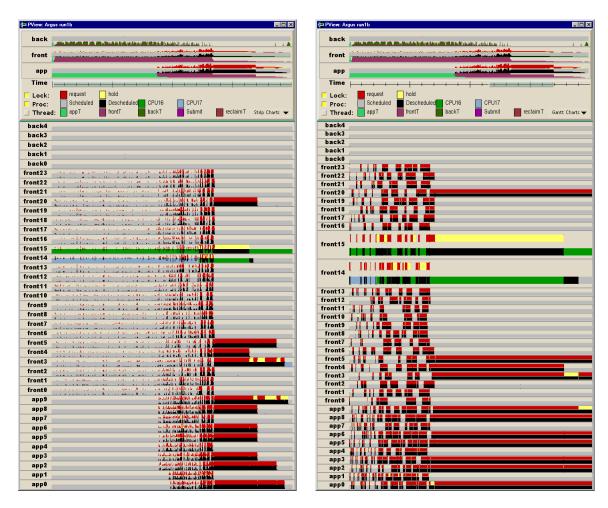

| 7.3 | PView visualization of Argus thread, process, and trap data | 69 |

|-----|-------------------------------------------------------------|----|

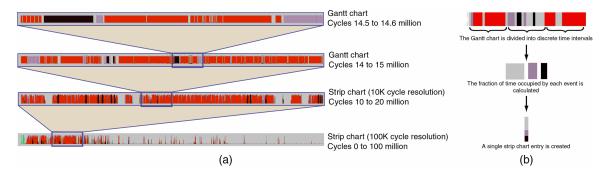

| 7.4 | Aggregation of event data into timeseries data              | 70 |

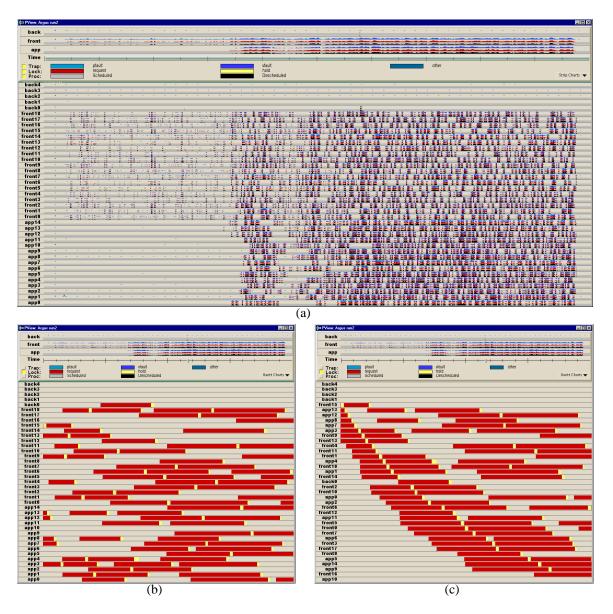

| 7.5 | PView visualization of Argus trap and kernel lock data      | 72 |

| 7.6 | Example of interactive sorting in PView                     | 74 |

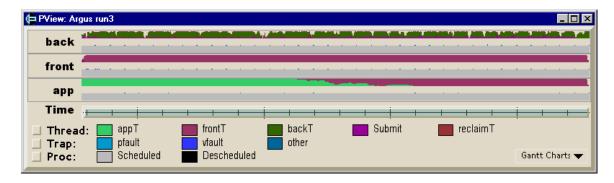

| 7.7 | PView summary view of improved version of Argus             | 76 |

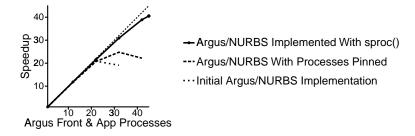

| 7.8 | Speedup curves for all versions of Argus                    | 76 |

## **Chapter 1**

## Introduction

This dissertation demonstrates that visualization can serve as an effective and integral tool for the analysis of computer systems. Visualization leverages the immense power and bandwidth of the human perceptual system and its pattern recognition capabilities, enabling interactive navigation of the large, complex data sets typical of computer systems analysis. In particular, the complexity and scale of modern systems frequently demands an exploratory data analysis process, in which the user has no a priori knowledge of the underlying problem; visualization is especially effective for this sort of analysis.

#### 1.1 The challenge: understanding complex systems

Computer systems are becoming increasingly complex due to both the growing number of users and their growing demand for functionality. For instance, the current generation of processors is built using tens of millions of transistors, employs a variety of complex implementation techniques such as out-of-order execution and speculation, and requires hundreds of man-years of development effort. Similarly, modern compute servers are composed of dozens or even hundreds of processors and include sophisticated memory systems and interconnection networks to provide peak performance. This increasing complexity magnifies the already difficult task developers face in exploiting the new technology.

In an attempt to cope with this complexity, system designers have developed new tools which are capable of capturing the behavior of these systems in great amounts of detail with minimal intrusiveness. Examples of these tools include:

**Complete machine simulation.** Complete machine simulators such as SimOS [27] model all of the hardware of a computer system in enough detail to boot and run a commercial operating

system. The simulator provides total, non-intrusive access to the complete hardware and software state of the system under simulation, from the contents of memory and caches down to the processor's functional units and registers.

**Real-time instrumentation.** Several systems use detailed hardware, firmware, and software instrumentation to monitor the performance of computer systems in real time. Compaq's Continuous Profiling Infrastructure [6] takes advantage of hardware counters implemented in the processor for profiling application performance; SGI's Performance Co-Pilot [53] uses both hardware counters and software counters stored by the operating system to provide a more complete picture of system behavior; and the FlashPoint protocol [20], implemented in firmware on the node controller of the FLASH multiprocessor [33], collects detailed memory system utilization statistics.

These rich data collection mechanisms present a formidable data analysis challenge: how can analysts explore and navigate the potentially huge data sets produced by these tools to achieve insight about the performance and behavior of the systems under study?

This challenge is typically addressed by reducing the data to produce a smaller, more manageable data set. This reduction can be achieved in several ways, such as statistical summarization, data aggregation, and restriction of the data collection to a very small subset of the available data. However, by essentially throwing away a large fraction of the data, the reduction approach fails to take full advantage of the power of the data collection tools.

An alternative, all-too-often used, approach is to dump data into large ad hoc text files, which are then analyzed manually. While this approach does preserve the richness of the data collection mechanism, attempting to find useful information in this data is often like trying to find a needle in a haystack: these trace or log files can easily run into the tens or hundreds of megabytes, and a full screen of text can display no more than several kilobytes of the data at a time.

These two techniques may be appropriate for answering very specific questions; however, they are less suited for understanding systems in the absence of presumptive knowledge of what to look for. Due to the complexity and scale of computer systems, the analysis process is typically an exploratory one, requiring analysts to search through the data in order to discover the underlying problem or bottleneck.

#### 1.2 The Rivet approach: interactive data exploration

Unlike the two approaches described above, information visualization is a compelling technique for the exploration and analysis of large and complex data sets. Visualization takes advantage of the immense power, bandwidth, and pattern recognition capabilities of the human visual system. It enables analysts to see large amounts of data in a single display, and to discover patterns, trends, and outliers within the data.

More importantly, an interactive visualization system enables analysts to retain the data provided by these rich data collection tools and navigate it in a manageable way. Beginning with a high-level summary of the data, analysts can progressively focus on smaller subsets of the data to be displayed in more detail, drilling down to the individual low-level data of interest. This exploratory data analysis and visualization process is succinctly characterized by Shneiderman's mantra for visual information seeking [52]: "Overview, zoom and filter, details-on-demand."

Visualization is not a novel approach for understanding computer systems; there have been several examples of visualizations of particular system components, developed for both pedagogical and analytical purposes. By far the most popular area for development has been the analysis of parallel applications running on message-passing multiprocessors [25, 59, 41]. However, visualizations have also been used for understanding processor performance [17, 1, 30], memory hierarchies [57, 14, 5], network utilization [19, 55], and so forth.

While these tools demonstrate the potential of visualization as an approach for gaining insights about the behavior of computer systems, they are essentially focused point-cases that are closely coupled with specific data collection tools and limited to displaying particular system components.

In order to take full advantage of rich and flexible data sources like the ones described in the preceding section, analysts need an equally powerful and flexible visualization system that can be learned once and applied to a wide variety of analysis tasks. The complexity of computer systems and the capabilities of the data collection tools place several demands on such a system:

- It must accept data from a wide variety of data sources. In particular, it must be able to import data from relatively free-form log files, which are frequently used in computer systems analysis.

- It must be able to manage and display large data sets, and enable users to manipulate this data and compute new derived data from it.

- It must support rapid prototyping. Analysts must be able to quickly generate visualizations of their data, or else they are unlikely to use the tool.

- It must be extensible. The complexity and diversity of computer systems make it impossible

to provide a comprehensive set of possible visualizations; users must be free to incorporate

their own components into the visualization environment.

In short, the system must enable an iterative, integrated analysis and visualization process. The exploratory data analysis process is a recurring cycle of hypothesis, experiment, and discovery, in which each data collection and analysis session answers some questions but raises new ones. The visualization system must enable users to adapt their visualizations as they proceed, incorporating new data and/or changing their data displays as needed.

This dissertation introduces Rivet, a general-purpose computer systems visualization environment designed to meet these demands. Rivet is a system that enables the rapid prototyping of sophisticated visualizations capable of efficiently displaying the large ad hoc data sets typically used in computer systems analysis.

The guiding principle in the development of Rivet is that the visualization process can be decomposed into a set of fundamental components, or building blocks. By identifying the building blocks and defining their interfaces, Rivet enables users to assemble sophisticated visualizations quickly by mixing and matching instances of these basic components.

In addition, this dissertation demonstrates the use of Rivet for constructing a variety of targeted visualizations for several different systems components and data sources. Rivet has been used to develop interactive visualizations for the real-time and post-mortem analysis of systems ranging from superscalar processors and memory systems to parallel applications and workstation clusters.

Finally, the rapid prototyping capability of Rivet can be used with comprehensive, configurable data sources like SimOS and PCP to provide a powerful framework for the ad hoc iterative analysis of computer systems as a whole.

#### 1.3 Organization of this dissertation

Chapter 2 introduces the Rivet visualization environment. It describes Rivet's modular architecture, which enables rapid prototyping of visualizations for a broad domain of computer systems problems, and its implementation, which provides this flexibility while achieving high performance.

Chapters 3 through 6 present case studies demonstrating the effectiveness of Rivet for the analysis of a variety of computer systems problems: (a) user-directed interactive parallelization using the SUIF compiler; (b) analysis of application memory system behavior as a function of processor, procedure, and data structure using the FlashPoint protocol on the FLASH multiprocessor; (c) analysis of the behavior of superscalar processors using two different detailed processor simulators; and (d) real-time monitoring of computer systems and clusters using the SimOS complete machine simulator and SGI's Performance Co-Pilot.

Each case study begins with an overview of the problem domain and the tools used for data

collection. This background information is followed by a description of the visualization itself, emphasizing features of Rivet that either enhanced the visualization or simplified its implementation. Each study concludes with examples of the visualization in action and a brief discussion of the visualization and related topics.

Chapter 7 presents a more detailed case study, showing how Rivet can be combined with rich data collection tools like SimOS to create a powerful framework that supports an iterative analysis and visualization process. The performance analysis of a parallel graphics rendering library, consisting of five simulation and visualization iterations, enabled the discovery of an unexpected interaction between the library and the operating system that was severely limiting the application's performance and scalability.

Chapter 8 reviews the major design decisions of Rivet in the context of the case studies and summarizes the contributions of the research presented in this dissertation.

## **Chapter 2**

## The Rivet Visualization Environment

This chapter describes the architecture and implementation of Rivet, a general-purpose environment for the development of computer systems visualizations. Rivet is designed to support the rapid prototyping of sophisticated data displays, enabling visualization to serve as an integral component of the analysis process.

The motivation for the development of Rivet is the observation that visualizations typically require a substantial implementation effort, and that in most cases analysts are unwilling to undertake such an effort. One of the main reasons for this difficulty is that visualizations are generally built directly on low-level graphics systems such as OpenGL, Tk, and X11. While these systems offer standard and convenient graphics rendering interfaces, they do not include support for many important visualization concepts and tasks.

The primary goal of Rivet is to provide an effective high-level graphics and data management infrastructure targeted for visualization development. Rivet is a powerful and flexible system that greatly simplifies the visualization design and implementation process, providing analysts with a single tool that can be learned once and applied to a wide range of computer systems problems.

Section 2.1 presents the modular architecture of Rivet, describing its fundamental building blocks and how they can be combined to create rich, interactive visualizations of data from a variety of sources.

Section 2.2 describes the implementation of Rivet, which provides the high-performance data management and graphics rendering capabilities required for real-world data analysis and visualization while retaining the flexibility of the architecture and enabling the rapid prototyping of visualizations.

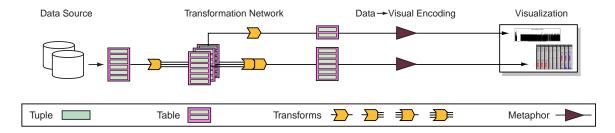

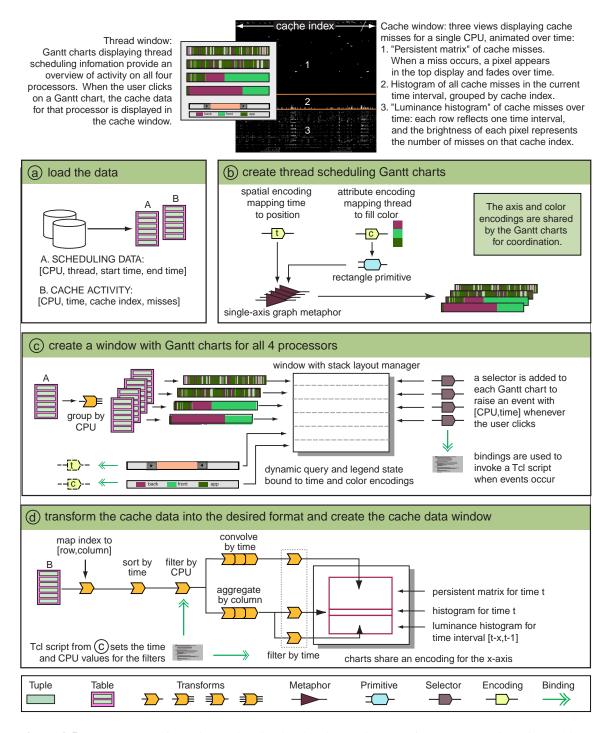

**Figure 2.1:** A schematic depiction of the information flow in Rivet. Data is read from an external data source and then passed through a transformation network, which performs operations such as sorting, filtering and aggregation. The resulting tables are passed to visual metaphors, which map the data tuples to visual representations on the display. Interaction and coordination are not shown here.

#### 2.1 Architecture

Figure 2.1 illustrates the basic stages of the visualization process: data is first imported, managed, and manipulated, and is then mapped into a visual representation that is presented to the user. In addition, most visualizations also support interaction with the data, its representations, and the mappings between them, as well as coordination between these components.

In computer systems visualizations focused on solving specific problems, these steps can be tightly integrated into a monolithic application. However, in order to make Rivet applicable to a wide range of problem domains, it uses a modular architecture. By exposing the interfaces of each step of the visualization process, Rivet allows users to combine components in many different ways to produce visualizations appropriate for different problems and data sources.

The remainder of this section presents the fundamental architectural components and how they are combined to form visualizations. After introducing the basic data objects and operations, the section presents the components that convert data into visual representations. Next comes a description of resource management and inter-object coordination mechanisms. The section concludes with a brief discussion of design decisions and the evolution of the Rivet architecture.

#### 2.1.1 Data management

#### Storage

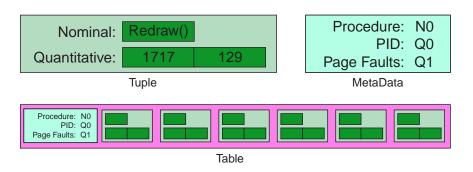

Rivet uses a simplified version of the relational data model. Figure 2.2 shows the primary data objects and their relationships.

The basic data element in Rivet is the *Tuple*, a collection of unordered data fields. Field values are categorized as either quantitative (continuous) or nominal (categorical); the former is stored as a floating-point value and the latter as a string.

Figure 2.2: Schematics of the primary Rivet data objects: Tuple, MetaData, and Table.

The data format of a tuple is described by a *MetaData* object. The metadata provides mappings from logical field names to the type and position of the corresponding data within the tuple. This separation of data objects into metadata and tuple enables tuples to remain relatively compact, an important factor for managing very large data sets.

Tuples with a common metadata format may be grouped together into a *Table*. The table is an abstract interface that supports operations such as iterating over tuples and querying data attributes such as minimum/maximum values (for quantitative fields) or sets of values (for nominal fields). The only current implementation of the table interface is the *DataVector*, a simple linear store of tuples; however, one could imagine more sophisticated implementations optimized for compact storage or rapid access.

This quasi-relational data model has the advantage of being relatively simple and familiar. In addition, the use of a single homogeneous data model provides a significant degree of flexibility in the construction of visualizations, allowing developers to create components that can operate on and display any data regardless of its source.

#### **Manipulation**

In addition to this basic data model, Rivet also includes support for data manipulation through the use of *Transform* objects. This native support for operating on and deriving new data directly within the visualization environment allows users to retain context and provides them with an integrated analysis and visualization platform.

As shown in Figure 2.1, transforms take one or more tables as input and produce one or more tables as output. While individual transforms are often quite simple, they can be dynamically composed to form a transformation network expressing a more complex operation. These transforms are active: any changes in the data are automatically propagated through the network. This property is especially useful for analyzing systems where the data can change in real time.

Rivet includes a set of standard transforms, including filtering, sorting, grouping, merging multiple tables, and joining tables together. However, since no system can hope to provide all operations users may need, developers may write their own transforms and incorporate them into their visualizations.

A compelling example of the importance of extensible transforms in Rivet is found in the mobile network analyses performed by Tang [55]. She incorporated several custom clustering algorithms into Rivet as transforms and visualized the results of applying the algorithms to the raw network data. By integrating the clustering code into Rivet, she could vary parameters of the algorithm and immediately see the impact on the visualization. This tight coupling facilitated a detailed exploration of the network data and provided a better understanding of the clustering algorithms themselves.

#### **Import**

Rivet is designed to import data from a variety of external sources. A family of *Parser* objects is used to convert this data into Rivet tuples and tables. Parser objects can read data from either text files or over sockets; the latter is especially useful for real-time monitoring.

The simplest parser implementation is the *CSVParser*, which takes text in character-separated value format and maps the columns of each line into fields of a tuple, returning a table as output.

While this parser works well for structured data, computer systems data is often stored in log files in an ad hoc format. For additional flexibility, Rivet also provides the *REParser*, which uses regular expressions to parse the input text. On a match, the parser can either map subexpressions directly to tuple fields or execute a user-defined piece of code (or *handler*) to process the data and create tuples.

Finally, Rivet also includes an *XMLParser*, which takes an XML file as input and executes user-defined handlers as it encounters start elements, character data, and end elements.

While the parsers provide a range of options for data import, these conversions can be relatively slow. To provide efficient access for repeated visualization sessions displaying a fixed data set, Rivet includes facilities for directly saving and loading tables using a binary data format.

#### Related work

Many visualization systems utilize a relational data model. The aspect of Rivet's data management that distinguishes it from existing systems is its extensive support for data transformations within the visualization environment. Several different approaches have been utilized by visualization systems to support data transformations.

Some systems, such as IVEE [3], rely on external SQL databases to provide data query and manipulation capabilities. However, as has been discussed in Goldstein et al. [21] and Gray et al. [22], the SQL query mechanism is limited and does not easily support the full range of visualization tasks, especially summarization and aggregation.

Visual programming and query-by-example systems such as Tioga-2 [4] and VQE [16] provide data transformations internal to the visualization environment. However, their transformation sets are not extensible by the user, and the existing transformations must be sufficiently simple to support the paradigm of visual programming.

IDES [21] and DEVise [36] are both very flexible systems that provide extensive data manipulation and filtering capabilities through interaction with the visual representations; however, neither is easily extensible by the user.

Data flow systems such as AVS [56], Data Explorer [37], Khoros [45], and VTK [50] closely match the flexibility and power offered by the data transformation components of Rivet, providing extensive pre-built transformations and support for custom transformations. However, their focus is on three-dimensional scientific visualization, and thus they do not provide data models and visual metaphors appropriate for computer systems study.

#### 2.1.2 Visual representation

#### **Data displays**

Once the data has been imported and transformed into a collection of data tables, the tables are displayed using one or more *Metaphors*. Metaphors create the visual representations for data tables using *Primitives*, which create the visual representations for individual tuples.

Specifically, a metaphor is responsible for drawing attributes common to the table, such as axes and labels. It also defines the coordinate space for the table: for every tuple in the table it computes a position and size, which are passed to the primitive along with the tuple. The primitive is then responsible for drawing the tuple within this bounding box.

In the simplest case, a metaphor uses a single primitive to draw each tuple. However, users may wish to distinguish subsets of the data within a metaphor; for instance, they may want to highlight or elide some tuples. This task is accomplished using *Selectors*, objects that identify data subsets. Metaphors may contain multiple selectors, each associated with a primitive to be used for displaying tuples in the specified subset. Selectors are described in more detail in Section 2.1.4.

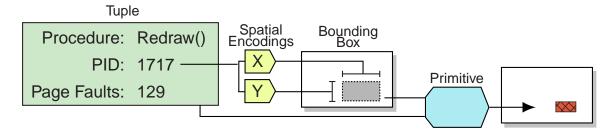

**Figure 2.3:** Rivet Metaphor schematic, showing the use of spatial encodings to lay out each tuple; in this example, the tuple's PID field determines its placement.

#### **Encodings from data to graphics**

Rivet uses *Encodings* to convert the data stored in a tuple into the elements of its visual representation. There are two general classes of encodings. Metaphors use *spatial encodings* to map fields of a data tuple to a spatial extent or location, and primitives use *attribute encodings* to map fields to retinal properties [10] such as color, fill pattern, and size.

Specifically, metaphors, shown in Figure 2.3, use one or more spatial encodings to determine the bounding box used by the primitive to render a given tuple. For example, a Gantt chart uses a single encoding to determine the horizontal extent of a tuple, while a two-dimensional scatterplot has separate spatial encodings for the horizontal and vertical axes. Because a spatial encoding can map any field or combination of fields in a tuple to a location, the metaphor itself is data independent.

Spatial encodings can be applied to both quantitative and nominal fields. Quantitative spatial encodings can be used to encode field values to locations using either a linear or logarithmic mapping; nominal spatial encodings can be used to assign fixed locations to individual domain elements, such as the entries in a bar chart.

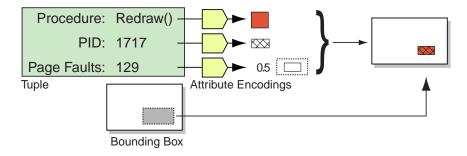

Primitives, shown in Figure 2.4, use several attribute encodings to determine the retinal properties of a tuple's visual representation. Using encodings provides great flexibility in how a tuple's contents can be mapped to a primitive: the user can selectively map any field or fields to any encoded retinal property of the primitive.

For example, most primitives include an encoding for their fill color, which can be used to represent some nominal or quantitative value stored in the tuple. For a nominal field such as process name, the user specifies a palette that maps values to colors. For a quantitative field such as number of cache misses, Rivet provides the isomorphic, segmented, and highlighting color encodings described by Rogowitz [47]; the user can choose whichever encoding is appropriate for the analysis task.

**Figure 2.4:** Rivet Primitive schematic, showing the use of attribute encodings to create each tuple's visual representation. In this example, the color, fill pattern, and relative size of the rectangle encode three different fields of the tuple.

#### User interface

In addition to the metaphors used to draw data tables, Rivet also includes a collection of standard user interface widgets: legends, menus, scrollbars, scales, list boxes, checkbuttons, and so on.

These interface objects are primarily used to configure encodings. For example, a color legend enables users to specify the color mappings in a palette, a range scale can be used to control the time interval displayed in a Gantt chart, and a pulldown menu can determine which data field is encoded into a particular spatial or retinal property.

#### **Related work**

The explicit mapping of individual data tuples directly to visual primitives first appeared in the APT [38] system, and has been used in numerous systems since, including Visage [49], DEVise [36] and Tioga-2 [4]. However, the use of selectors to map sets of tuples to different visual primitives is unique to the Rivet visualization environment.

The use of encodings to parameterize visual metaphors and primitives is another innovation of the APT system. In APT and in subsequent systems such as Visage, encodings formalize the expressive capabilities of visual representations and are utilized by knowledge-based systems to automatically generate graphical displays of information. Experiences with Rivet have shown that encodings also provide an ideal parameterization for visual representations within a programmable visualization environment.

#### 2.1.3 Display resource management

Rivet provides several mechanisms for allocating display resources such as drawing time and screen space among metaphors.

Redraw Managers regulate the metaphor rendering process by allocating drawing time to each metaphor. Under the basic redraw manager, metaphors are given an unlimited amount of time to render their displays. However, more complex redraw managers may be used to restrict drawing times in order to provide smooth animation or interactivity for large data sets. These managers actively monitor and distribute time amongst metaphors. For instance, if the user is interacting with a particular metaphor, a redraw manager might allocate more drawing time to it. A metaphor can adapt to its allocation of time in a variety of ways, such as reducing its level of detail or omitting ornamentation.

Layout Managers control the distribution of screen space among multiple metaphors within a window. The layout manager assigns each metaphor a position in the window, and enables users to move and resize metaphors through direct manipulation. Rivet includes several layout managers that utilize different techniques for allocating screen space to each metaphor. The default FreeFormLayoutMgr, based on Tk's "placer" geometry manager, uses a combination of absolute and parent-relative geometry to specify the location of each metaphor; the GridLayoutMgr assigns metaphors locations in a regular grid; the StackLayoutMgr lays out metaphors in a one-dimensional array, and enables users to change the relative size and position of metaphors within the stack; and the TreeMapLayoutMgr is used to draw hierarchies of metaphors using the squarified treemap [11] layout algorithm.

Finally, Rivet includes a set of *Device Managers*, which handle interactions between Rivet and the underlying system. The device managers encapsulate platform-specific operations such as receiving user input and interfacing with the window manager. This encapsulation makes Rivet easily portable to different platforms; to date, Rivet has been used on UNIX/X11, Microsoft Windows, and Stanford's Interactive Mural [28].

#### 2.1.4 Coordination

Rivet enables coordination between objects in three ways: the listener mechanism, support for events and bindings, and the use of selectors. Figure 2.5 provides an example showing how a coordinated multiple-view visualization can be developed using these techniques.

#### Listeners

The modular architecture of Rivet enables a significant amount of coordination simply through object sharing. For example, metaphors can share a selector to enable *brushing*, in which specified data subsets are highlighted in the same way across different displays. Metaphors can also share a spatial encoding to provide a common axis, or they can share a primitive to ensure a consistent visual representation of data across views.

However, shared objects must stay consistent. All objects in Rivet participate in the listener mechanism: objects dependent on other objects "listen" for changes. When an object is notified, it updates itself to reflect the change. For example, when a metaphor's spatial encoding is modified, the metaphor recomputes the bounding boxes for the tuples in its table. In addition to this simple example, the listener model easily enables other features such as animation and active transformation networks.

While the listener mechanism is powerful, some situations require more sophisticated coordination between objects. To handle these cases, Rivet provides two mechanisms: bindings and selectors.

#### **Bindings**

Rivet objects can raise events to indicate when actions of interest occur. Bindings allow users to execute an arbitrary sequence of operations whenever a specific object raises a particular event. For instance, a metaphor may raise an event when a mouse click occurs within its borders, reporting that a tuple has been selected; a binding on this event could display the contents of the selected tuple in a separate view.

#### **Selectors**

Selectors, introduced earlier, separate the selection process into two stages: the selection stage and the query stage. The first stage corresponds to the actions performed when selection occurs, such as raising an event or recording the tuple being selected. The second stage refers to querying the selector as to whether a tuple is selected. Metaphors use this second stage in deciding whether to elide or highlight a tuple, as described in Section 2.1.2.

#### **Related work**

North's taxonomy of multiple window coordination [42] identifies three major types of coordination:

- Coupling selection in one view with selection in another view

- Coupling navigation in one view with navigation in another view

- Coupling selection in one view with navigation in another view

Whereas many visualization systems provide some form of coordination, the binding and selector mechanisms enable Rivet to support all three forms of coordination.

**Figure 2.5:** An example of creating a visualization in Rivet, using data from the execution of a multiprocessing application. The visualization consists of coordinated views of thread scheduling behavior and cache miss data.

Both the Visage and DEVise visualization environments provide extensive coordination support: Visage includes a well-architected direct manipulation environment for inter-view coordination, and DEVise uses cursors and links to implement inter-view navigation and selection. Whereas these implementations of coordination have highly refined user interface characteristics, Rivet's programmatic coordination architecture is more expressive and flexible.

The Snap-Together Visualization project [43] presents a cohesive architecture for coordination, focusing only on the integration of numerous compiled components into a cohesive visualization. It does not, however, provide support for developing the visualizations themselves.

#### 2.1.5 Architecture discussion

Choosing interfaces to enable maximal object reuse was the main challenge underlying many design choices, including:

- 1. The separation of data objects from visual objects

- 2. The homogeneous data model

- 3. The use of encodings

- 4. The separation of visual metaphors from primitives

- 5. The abstraction of selectors into a separate object

These choices give rise to much of the functionality in Rivet. For example, the first two choices allow any data to be displayed using any visual metaphor: one visualization can have multiple views of the same data, and conversely, the same metaphor can be used to display different data sets. The second choice also enables users to build arbitrary transformation networks. The next two choices allow the user to explicitly define the mapping from data space to visual space: primitives use retinal encodings to display any data tuple, irrespective of dimensionality or type, and metaphors use spatial encodings to lay out any primitive. The last choice permits the user to have multiple views of different selected subsets of the same data; it also allows metaphors to be reused with a different interaction simply by changing selectors.

Several iterations were made during the evolution of the Rivet architecture. Whereas previous Rivet implementations were more monolithic, resulting in an inability to easily change the imported data or visualizations, this modular architecture with a relatively small granularity and shareable objects has produced an easily configurable visualization environment applicable to a wide range of real-world computer systems problems.

#### 2.2 Implementation

The design goals of Rivet place two fundamental constraints on its implementation. First, visualizing the large, complex data sets typical of computer systems requires Rivet to be fast and efficient. Second, the desire for flexibility in the development and configuration of visualizations requires Rivet to export a readily accessible interface. This section discusses these two implementation challenges and how they are addressed in Rivet.

#### 2.2.1 Performance

In order to support interactive visualizations of computer systems data, a visualization system must be able to efficiently display very large data sets. An early implementation of Rivet, done entirely in Tcl/Tk, was flexible but unable to scale beyond small data sets due to the performance limitations of the Tcl interpreter and the Tk graphics library. Consequently, the Rivet implementation now uses C++ and OpenGL.

C++ is a good match for the object-oriented architecture of Rivet. In addition, it enables Rivet to take advantage of the Standard Template Library (STL), greatly simplifying the implementation of its data structures.

OpenGL is a widely used standard for the implementation of sophisticated graphics displays. It achieves high performance through hardware acceleration and is platform independent, unlike windowing systems such as X11. Furthermore, using OpenGL enables Rivet to run on the Interactive Mural [28], which provides a large, contiguous screen space and support for collaborative interaction.

However, there were several challenges in enabling the modular architecture of Rivet to take full advantage of the high performance OpenGL offers. Specifically, attempts to assign each graphical object (metaphor and user interface object) its own independent OpenGL context or viewport did not scale. While OpenGL can in principle support large numbers of contexts and viewports, in practice its performance severely degrades when using more than a few. In order to support a large number of graphical objects within a single visualization, Rivet now assigns a single context and viewport to each window, and uses OpenGL's matrix transformations and clipping support to restrict each object to its drawing region within the window.

In addition, Rivet uses two other techniques to improve its rendering performance. First, when a subregion of a window changes, Rivet computes the minimal set of graphical objects that must be redrawn to update the display. Second, objects use OpenGL display lists to store the list of graphics commands they issued; if an object must be redrawn but its underlying data is unchanged, the display list can be used for faster rendering.

Support for all of these techniques is provided in the graphical object base class, so particular metaphors and user interface objects can be implemented without knowledge of these details.

#### 2.2.2 Flexibility

While all of the objects described in Section 2.1 are implemented in C++ for performance, Rivet, like several other visualization systems [50, 24, 51], uses a scripting language to provide a more flexible mechanism for rapidly developing, modifying, and extending visualizations.

Rivet uses the Simplified Wrapper and Interface Generator (SWIG) [8] to automatically export the C++ object interfaces to standard scripting languages such as Tcl, Perl, or Python. SWIG greatly simplifies the tedious task of generating these interfaces and provides a degree of scripting language independence.

Since all Rivet object APIs are exported through SWIG, users can create visualizations by writing scripts that instantiate objects, establish relationships between objects, and bind actions to object events.

One potential pitfall when using a scripting language is the performance cost: the interpreter can quickly become a bottleneck if it is invoked too frequently, especially in the main event loop. However, in Rivet, high-frequency interactions between objects are handled by the listener and selector mechanisms, which completely bypass the interpreter. While the binding mechanism relies on the interpreter to execute scripts bound to events, bindings are typically used to respond to user interactions, which are relatively infrequent (from the point of view of the system). Thus, Rivet is able to realize the benefits of flexibility without suffering a significant performance cost.

#### 2.3 Summary

The Rivet visualization environment is a cohesive platform for the analysis and visualization of modern computer systems. It uses a component-based architecture in which complex visualizations can be composed from simple data objects, visual objects, and data transformations. Rivet also provides powerful coordination mechanisms, which can be used to add extensive interactivity to the resulting visualizations. The object interfaces chosen in the design of Rivet demonstrate how, with the proper parameterization, the design of a sophisticated and interactive visualization can be a relatively simple task.

## Chapter 3

## Interactive Parallelization: SUIF Explorer

With the growing availability and popularity of large-scale multiprocessor systems containing dozens or hundreds of processors, there is an increasing demand for applications capable of taking full advantage of the computational power of these systems. Consequently, an important area of compiler research is the field of parallelizing compilers, which enable standard sequential applications to run in parallel.

This chapter describes the use of Rivet as a component of SUIF Explorer [35], an interactive parallelizer that couples compiler optimizations and feedback with profiling data and guides the user through the parallelization process.

#### 3.1 Background

Exploiting coarse-grain parallelism is critical to achieving good performance for existing sequential programs running on multiprocessors. While automated parallelization can sometimes achieve good performance, a parallelizing compiler is limited by its lack of application-specific knowledge. On the other hand, because of the size and complexity of legacy codes, manual parallelization is often a challenging and error-prone task.

Interactive parallelizing compilers such as ParaScope [23] and SUIF Explorer [35] combine the advantages of automatic and manual techniques. These systems use sophisticated static compiler analyses to parallelize code sequences where possible. When automated parallelization fails, these systems make the analysis results available to the programmer, who can combine this information with his knowledge of the application to uncover additional coarse-grain parallelism in the code.

| II | First Line | Last Line | Parallel | Coverage | Granularity | Promising | Depth |

|----|------------|-----------|----------|----------|-------------|-----------|-------|

|    | 1 83       | 130       | N        | 97.7587% | 1504853.625 | Y         | 1     |

| ,  | 2 91       | 130       | N        | 97.7587% | 1504853.625 | N         | 2     |

|    | 3 146      | 153       | Y        | 0.0116%  | 178.082     |           | 1     |

| (  | 5 160      | 168       | N        | 1.7973%  | 27667.582   | Y         | 1     |

| ,  | 7 162      | 168       | N        | 1.7973%  | 5533.515    | Y         | 2     |

| ;  | 3 164      | 168       | N        | 1.7973%  | 86.461      | Y         | 3     |

| 9  | 9 166      | 168       | N        | 1.8176%  | 1.410       | N         | 4     |

|    | : :        | :         | :        | :        | :           | :         | :     |

**Table 3.1:** Sample output produced by SUIF Explorer's dynamic analysis tools.

In addition to this static analysis, systems such as SUIF Explorer and the D System [2] use a set of dynamic execution analyzers to find sections of code which are potentially parallelizable and to determine which regions of the program would most benefit from parallelization. This information is used to guide the analysis, enabling the programmer to focus on the sections of code where user intervention will help the most.

Specifically, the dynamic analyses performed by SUIF Explorer report the following data for each loop in a program:

**Parallel.** Whether the loop can be parallelized by the compiler. Only loops that are not automatically parallelized require user intervention.

**Coverage.** Percentage of execution time spent in the loop. Parallelizing loops with high coverage yields the most benefit.

**Granularity.** The amount of parallel execution time between synchronization points. Parallelizing coarse-grain outer loops instead of fine-grain inner loops reduces overheads and improves performance.

**Promising.** Whether the loop is likely to benefit from user intervention.

**Depth.** The dynamic nesting depth of the loop during program execution.

This information is summarized by the compiler in a single table like the one shown in Table 3.1.

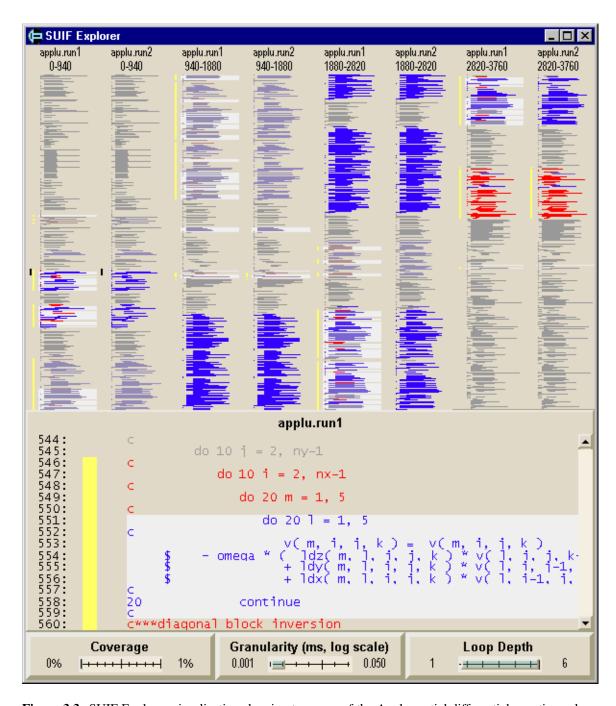

#### 3.2 Visualization

Figure 3.1 shows an example of the visualization of this data developed within Rivet and integrated into the SUIF Explorer system. The visualization presents two linked views of the application's source code, along with a set of sliders that allow the user to configure the data display.

**Figure 3.1:** Screenshot of the SUIF Explorer visualization, combining a bird's-eye code overview with a detailed source code view. The three range sliders enable the user to interactively filter and highlight sections of code. Lines are color-coded according to the dynamic execution analysis results.

#### 3.2.1 Overview

The top pane presents a bird's-eye overview, inspired by the SeeSoft [18] system, of the complete source code of the application: each line of code is represented by a line segment whose indentation and length matches that of the program text. The color of the line indicates its parallelization status: blue for a parallel loop, red for a sequential loop that was not parallelized, and gray for sequential non-loop code that can never be run in parallel. In addition, some loops are drawn with a gray background; this highlight is an indication of loop granularity and will be discussed in more detail below. Finally, sections of code that are identified as promising for user intervention are highlighted using a vertical yellow bar.

#### 3.2.2 Source view

The bottom pane is a simple source code browser. A vertical black bar in the overview identifies the lines being displayed; the user can navigate the code either by using the scrollbar or by directly selecting a section of code in the overview. The source view uses the same color encodings as the overview for conveying parallelization information.

#### 3.2.3 Controls

The bottom of the display consists of three range sliders used to filter and highlight the data in the other two panes; these dynamic query sliders provide continuous feedback, updating the display as the user adjusts them.

The Coverage slider controls the shades of red and blue used to draw the loops. Loops within the specified coverage range are drawn using an isomorphic color ramp, in which the saturation and brightness of the colors increase linearly with coverage; colors outside the range are clamped to the low/high values. This color ramp draws attention to the most important sections of code: loops which use the most execution time are visually prominent, and low-coverage loops which have little impact on running time tend to fade into the background.

As it turned out, the ramp feature proved to be quite subtle and not as useful as hoped. In fact, users typically collapsed the range of the color ramp down to a single value, effectively turning the control into a filter that hides loops below the chosen coverage threshold. Users would then drag the filter up from the low end of the scale, causing less interesting loops to disappear one by one from the foreground.

The Granularity slider controls the gray background box mentioned above. The user specifies a granularity range, and all loops falling within that range are highlighted in gray. This technique enables users to distinguish between coarse-grain parallel loops, which generally perform well, and

fine-grain parallel loops, whose high synchronization overheads often make them good candidates for user attention.

The Loop Depth slider filters the data according to dynamic loop depth: the visualization only displays data for loops within the specified depth range. This slider can be used to selectively focus attention on inner loops, which are typically easier to parallelize, or on outer loops, which provide the most benefit when parallelized.

#### 3.3 Rivet features

This visualization demonstrates several important features of Rivet's modular architecture and its coordination mechanisms.

First, visualization developers can combine simple building block objects in different ways to produce a variety of data displays. For example, while the overview and source view look quite different, they are both implemented using the same metaphor: a simple one-column table. Each view has its own spatial encoding that uses the source code's line number to determine its position in the table. While the overview's encoding maps the entire program text into the table, the source view only maps a small portion of the source code to its display.

Aside from the spatial encodings, the two views differ only in their choice of primitive: the overview encodes the indentation and length of each line of code as a rectangle, while the source view directly displays the program text.

Second, the sharing of objects enables developers to create coordinated multiple-view visualizations. While the high-level overview and line-by-line source view use different primitives, these primitives share a single set of foreground and background color encodings for displaying the performance data for each line of code. The shared encodings provide a consistent representation of data in both views.

Finally, this example shows how Rivet's event binding and listener mechanisms enable users to interact with visualizations and explore their data. When users adjust the Coverage and Granularity sliders, an event binding updates the foreground and background color encodings respectively. The listener mechanism automatically propagates these changes, causing both the overview and source view to refresh their displays using the new encoding values, thus providing instant visual feedback.

#### 3.4 Examples

The SUIF Explorer system has been used to dramatically improve the performance of several scientific applications. Two examples are shown in Figures 3.2 and 3.3.

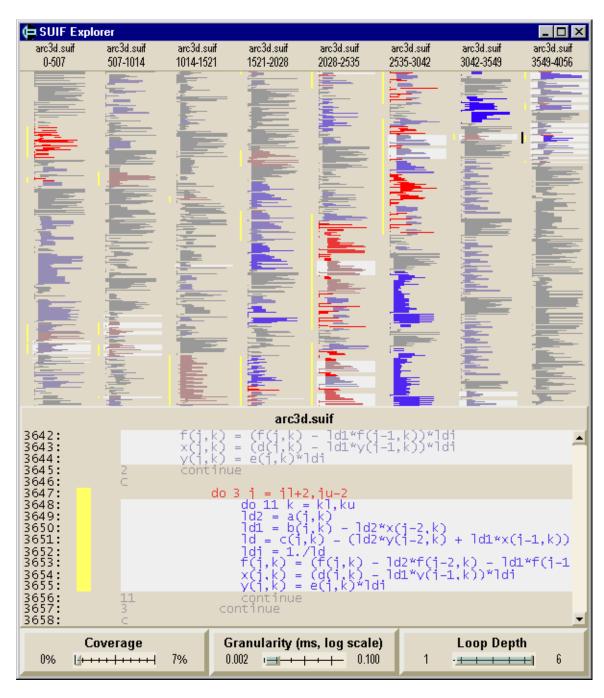

**Figure 3.2:** SUIF Explorer visualization showing three runs of the MDG molecular dynamics application, demonstrating how user intervention improved the parallel coverage of the application.

### 3.4.1 MDG

Figure 3.2 shows a side-by-side comparison of three successive compilations of MDG, a molecular dynamics model. Each run is split into several columns, with the columns interleaved to facilitate comparisons. The first column shows the results of MDG when compiled using SUIF alone without user intervention. While the compiler succeeds in parallelizing 73% of the computation, the combination of Amdahl's law and parallelization overheads cause the application to show no speedup at all on a four-processor machine.

In the visualization, the Coverage slider is set to de-emphasize low-coverage loops responsible for less than 15% of the total running time; the resulting display shows two major loop nests in the final column. In both nests, the compiler has only parallelized several small inner loops (shown in blue); the enclosing outer loops (red with yellow highlight) could not be automatically parallelized, but were found to be promising candidates for user intervention.

The second and third runs of the program show the results after the user has interacted with SUIF Explorer, applying his knowledge of the application to enable the compiler to parallelize both loops. With nearly all of the execution time spent in coarse-grain parallel loops (highlighted using the Granularity slider), the final version of the program achieves full linear speedup on four processors and a speedup of 6.0 on eight processors.

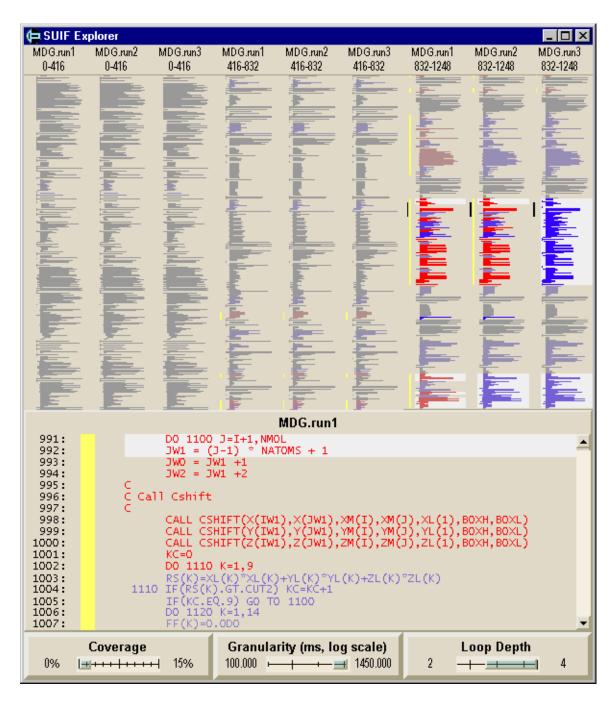

#### **3.4.2** Applu

Figure 3.3 shows the performance data for Applu, a partial differential equation solver, before and after the use of SUIF Explorer. In this example, SUIF alone succeeds in achieving 95% parallel coverage for the application; however, the program still does not achieve good overall speedup.

The problem in this case is demonstrated by using the Granularity slider to emphasize fine-grain loops. In the initial version of the program, many of the loops are highlighted in gray, indicating that they run in parallel for less than a twentieth of a millisecond between synchronization points; this synchronization overhead is the reason for the poor performance.

Once again, in this case SUIF Explorer has found that the enclosing outer loops are promising candidates for further examination. After user intervention, the compiler successfully parallelizes them, and the resulting coarse-grain parallelism enables the program to run with a superlinear speedup of 4.5 on four processors.

**Figure 3.3:** SUIF Explorer visualization showing two runs of the Applu partial differential equation solver, demonstrating how user intervention improved the parallelism granularity of the application.

# 3.5 Discussion

The visual presentation of the data provided by SUIF Explorer offers several benefits over the raw table of numbers shown in Table 3.1:

- It presents the loop execution data directly in the context of the application's source code, rather than in terms of loop ID numbers and program line numbers.

- It focuses user attention on the sections of code most likely to benefit from user interaction.

- It enables the user to interactively filter the data, eliminating uninteresting code sequences.

- It facilitates comparisons between multiple runs of the same program.

One limitation of the visualization is that it is not fully integrated into SUIF Explorer. Because Rivet is designed to be a stand-alone system, it communicates with the rest of SUIF Explorer using a socket. SUIF Explorer provides the profiling data to Rivet, the user interacts with Rivet to identify the sections of code they wish to examine, and Rivet notifies Explorer of the user's interactions; further interaction with the compiler is then performed directly in the SUIF Explorer environment. Fortunately, users have found this loose coupling to be satisfactory; while a fully-integrated solution would be preferable, it would also require a significant additional implementation effort.

# **Chapter 4**

# **Memory Profiling: Thor**

Like the SUIF Explorer example in the previous chapter, the visualization presented in this chapter addresses the challenge of maximizing the performance of programs running in parallel; in this case, the emphasis is on tuning the memory system performance of applications.

The Thor visualization presents detailed memory system utilization data collected by the Flash-Point [20] memory profiler. Thor employs interactive data filtering and aggregation techniques, enabling users to drill down from an overview of an application's memory system performance to detailed displays showing memory requests for individual processors, procedures, and data structures.

# 4.1 Background

Over the years, processing speed has continued to grow at an exponential rate as described by Moore's Law. However, the performance of the memory system that transfers data into and out of the processor has been improving at a much slower rate. Consequently, memory system performance has a large and growing impact on application performance; in fact, for many applications, it is the primary performance bottleneck.

This problem is even more acute on cache-coherent shared-memory multiprocessors. The large scale of these machines and the distribution of memory across all nodes of the machine serve to increase the latency of remote memory accesses. While the shared-memory programming model allows developers to write parallel applications without performing explicit memory placement, in order to maximize performance it is often necessary for them to understand and control the layout of data structures in memory.

To help programmers better understand and improve the memory system performance of their

applications, several memory profiling systems have been developed. One such example is Flash-Point [20], a firmware memory profiler that runs on the FLASH multiprocessor [33].

FlashPoint takes advantage of FLASH's programmable node controller, running directly on the controller in tandem with the base cache coherence protocol. Consequently, FlashPoint is able to collect detailed data about every cache and translation lookaside buffer (TLB) miss taken by an application, and it can attribute each miss to the application procedure and data structure responsible. FlashPoint further classifies all requests as reads or writes, and identifies whether the requests are to local or remote memory; it can also keep track of the number of compulsory and coherence misses, along with interventions and three-hop misses in which the data must be retrieved from another processor's cache. The implementation of FlashPoint enables it to record and classify this data with very low overhead, providing users with detailed real-time memory profiling with minimal impact on application behavior.

# 4.2 Visualization

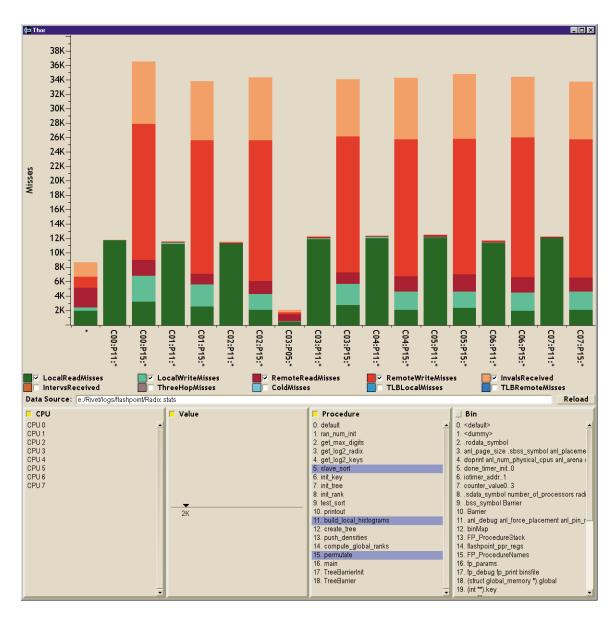

The Thor visualization, shown in Figure 4.1, is an interface to the data collected by FlashPoint. It combines a relatively simple visual representation with a set of controls for interactively aggregating, filtering, and sorting the data.

The top half of the figure displays a stacked bar chart showing the total number of memory requests attributed to each CPU, procedure, and data structure (or bin), with each bar color-coded according to the type of request. Directly beneath the chart is a legend: each request type is shown along with its color (the user can click on the color to change it) and a check box (the user can toggle it to include or exclude the type from the bar chart). The user can drag and drop legend entries to change the stacking order of the bars in the chart.

FlashPoint collects far too much data for Thor to show a full bar chart of every CPU-procedurebin triple: even a relatively simple application with a dozen procedures and bins running on an eight-processor machine would require over one thousand entries. To manage this complexity, Thor provides two forms of data aggregation:

**Category aggregation.** The user can choose to aggregate the data over all CPUs, procedures, or bins, providing a less detailed but more easily understood display. In Figure 4.1, for example, the user has aggregated the data on the bin field; the resulting chart shows the distribution of misses over CPU-procedure pairs, with an asterisk in place of the bin label to indicate the bin aggregation.

**Threshold aggregation.** The user can specify a minimum miss threshold; all chart entries with fewer misses are aggregated into a single "other" entry, indicated in the chart with a single

**Figure 4.1:** Screenshot of the Thor visualization of FlashPoint memory profiling data, displaying a bar chart of cache misses color-coded by miss type and broken down by the processor, procedure, and data structure responsible for the misses. The color legend enables users to filter and sort the cache miss categories; the lists at the bottom of the window enable users to filter and sort the contents of the chart.

asterisk. In Figure 4.1, a miss threshold of 2000 aggregates seven small CPU-procedure pairs into the single entry at the far left end of the chart.

At the bottom of the display are four controls: three listboxes and a slider. These controls serve several purposes. First, the yellow check boxes in the upper left corner of the controls are used to enable and disable both category and threshold aggregation in the chart; for the latter, the Value slider is used to specify the minimum miss threshold. Second, the listboxes display mappings from the procedure and bin indices used in the chart to the actual names used in the program. The entries themselves can also be used to filter the data display: if the user selects one or more entries in the listbox, only the data corresponding to those entries will be shown in the chart. In the figure, the user has selected procedures 5, 11, and 15, further reducing the complexity of the chart. Finally, the user can drag and drop the controls to specify the bar ordering; in this case, the bars are sorted first by CPU, then by the number of misses, then by procedure and bin number.

# 4.3 Rivet features

The Thor visualization demonstrates the power and flexibility of Rivet's data transformation mechanism, along with its support for interactive data exploration.

Each of the data operations described above — category aggregation, threshold aggregation, filtering, and sorting — is implemented as a Rivet transform. Thor combines these primitive operations into a transformation network that processes the raw FlashPoint data as desired by the user and assigns the resulting table to a stacked bar chart metaphor for display.

When the user explores the data by interacting with the visualization controls, the Rivet listener and event binding mechanisms update the display: event bindings reconfigure the transforms in response to the user's interactions, and the listener mechanism triggers a recomputation of the transformation network and subsequent redraw of the data display. An additional event binding queries the resulting data for its maximum value and rescales the chart accordingly.

# 4.4 Examples

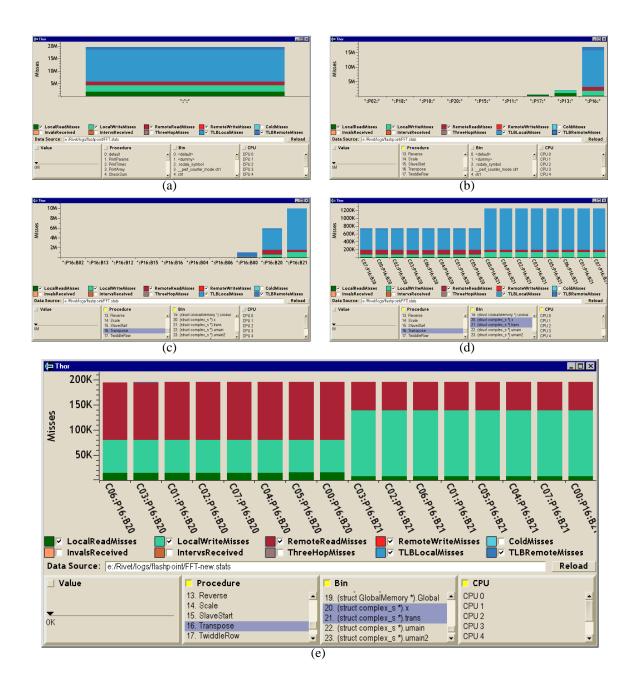

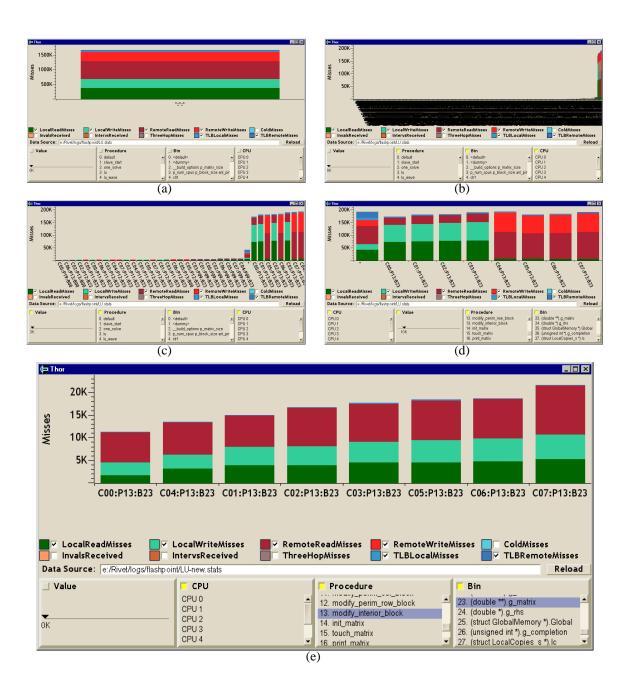

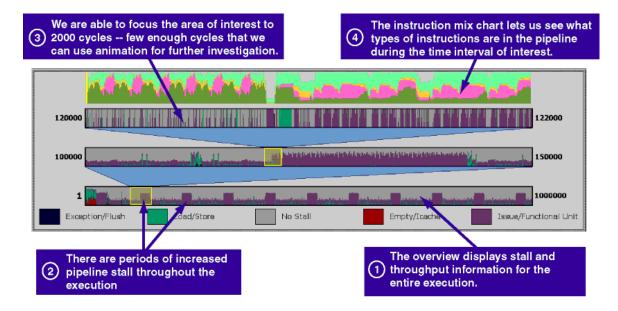

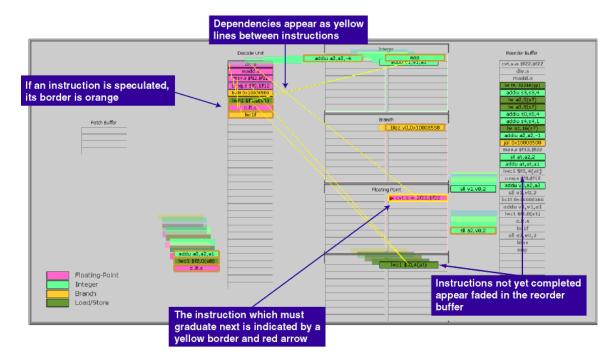

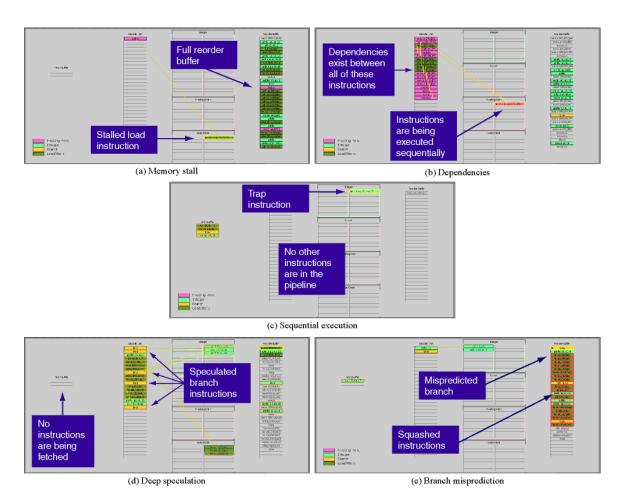

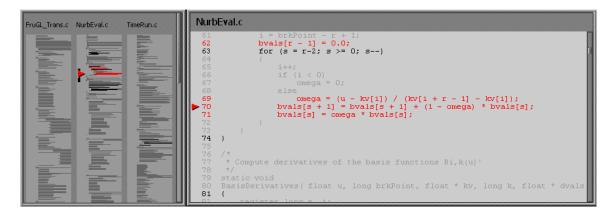

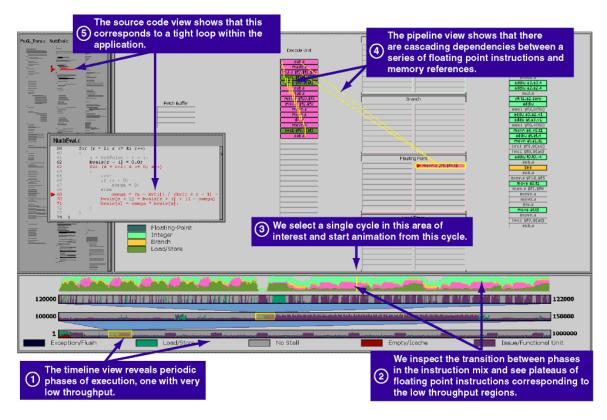

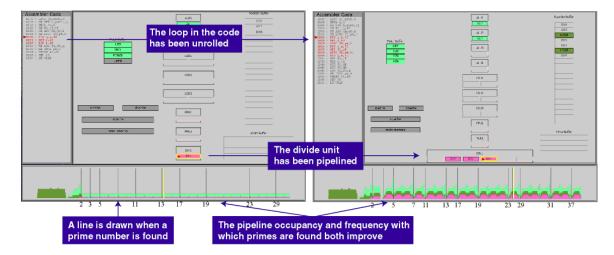

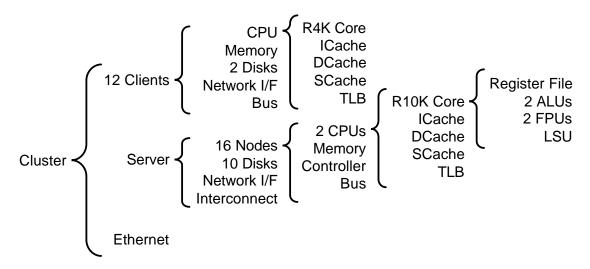

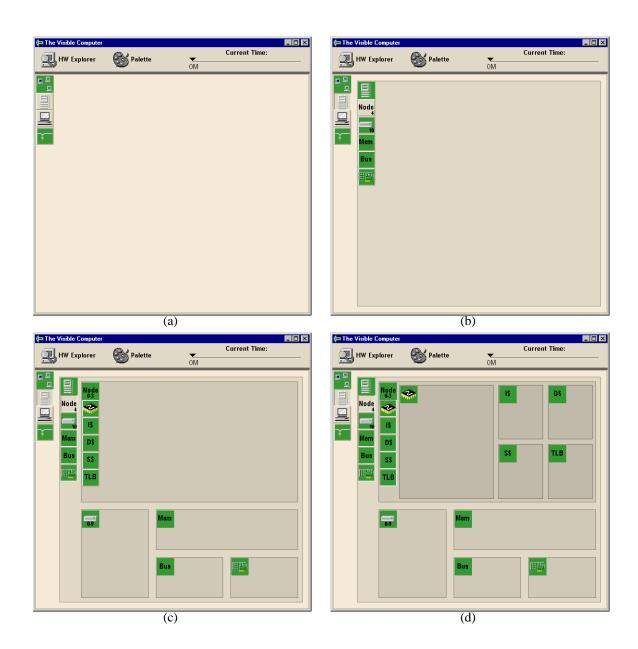

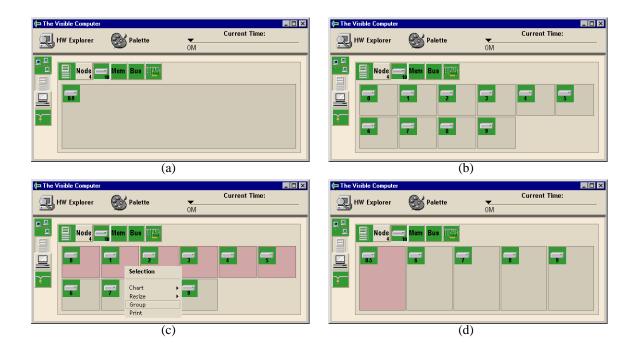

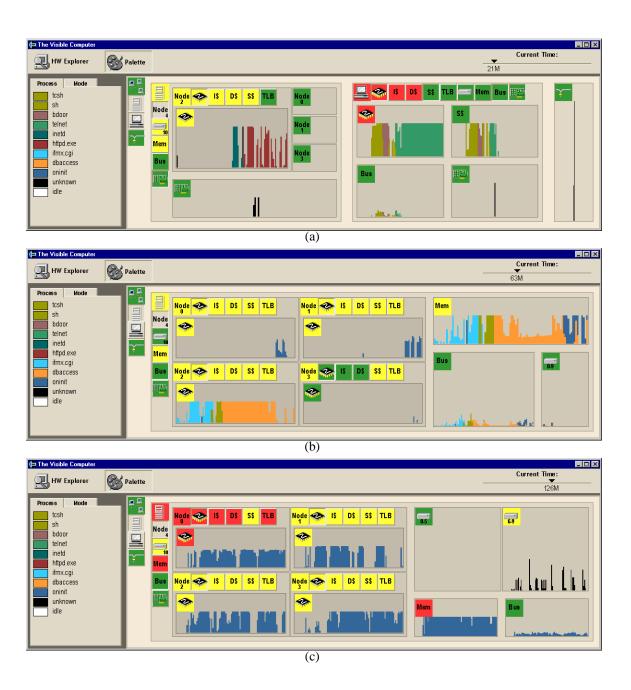

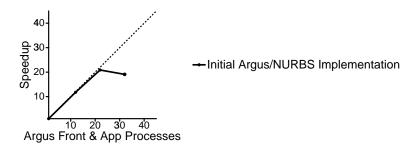

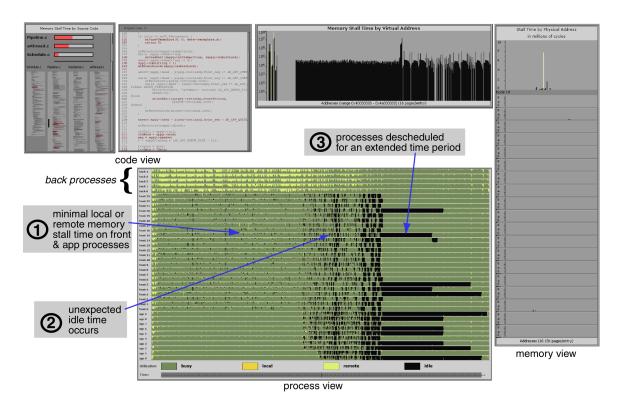

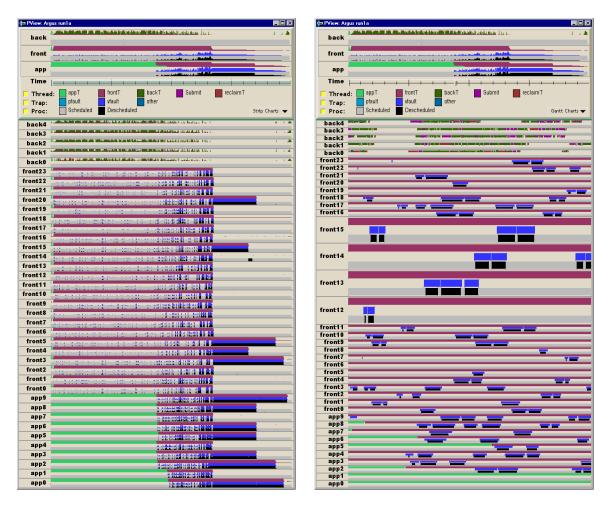

#### **4.4.1 FFT**