# DESIGNING GRAPHICS ARCHITECTURES AROUND SCALABILITY AND COMMUNICATION

#### A DISSERTATION

SUBMITTED TO THE DEPARTMENT OF ELECTRICAL ENGINEERING

AND THE COMMITTEE ON GRADUATE STUDIES

OF STANFORD UNIVERSITY

IN PARTIAL FULFILLMENT OF THE REQUIREMENTS

FOR THE DEGREE OF

DOCTOR OF PHILOSOPHY

Matthew Eldridge

June 2001

© Copyright by Matthew Eldridge 2001 All Rights Reserved

| I certify that I have read this dissertation and that in my opin- |

|-------------------------------------------------------------------|

| ion it is fully adequate, in scope and quality, as a dissertation |

| for the degree of Doctor of Philosophy.                           |

#### Pat Hanrahan (Principal Adviser)

I certify that I have read this dissertation and that in my opinion it is fully adequate, in scope and quality, as a dissertation for the degree of Doctor of Philosophy.

#### William J. Dally

I certify that I have read this dissertation and that in my opinion it is fully adequate, in scope and quality, as a dissertation for the degree of Doctor of Philosophy.

#### Mark Horowitz

Approved for the University Committee on Graduate Studies:

### **Abstract**

Communication forms the backbone of parallel graphics, allowing multiple functional units to cooperate to render images. The cost of this communication, both in system resources and money, is the primary limit to parallelism. We examine the use of object and image parallelism and describe architectures in terms of the *sorting* communication that connects these forms of parallelism. We introduce an extended taxonomy of parallel graphics architecture that more fully distinguishes architectures based on their sorting communication, paying particular attention to the difference between sorting *fragments* after rasterization, and sorting samples after fragments are merged with the framebuffer. We introduce three new forms of communication, distribution, routing and texturing, in addition to sorting. Distribution connects object parallel pipeline stages, routing connects image parallel pipeline stages, and texturing connects untextured fragments with texture memory. All of these types of communication allow the parallelism of successive pipeline stages to be decoupled, and thus load-balanced. We generalize communication to include not only interconnect, which provides communication across space, but also memory, which functions as communication across time. We examine a number of architectures from this communicationcentric perspective, and discuss the limits to their scalability. We draw conclusions to the limits of both image parallelism and broadcast communication and suggest architectures that avoid these limitations.

We describe a new parallel graphics architecture called "Pomegranate", which is designed around efficient and scalable communication. Pomegranate provides scalable input bandwidth, triangle rate, pixel rate, texture memory and display bandwidth. The basic unit of scalability is a single graphics pipeline, and up to 64 such units may be combined.

Pomegranate's scalability is achieved with a novel "sort-everywhere" architecture that distributes work in a balanced fashion at every stage of the pipeline, keeping the amount of work performed by each pipeline uniform as the system scales. The use of one-to-one communication, instead of broadcast, as well as a carefully balanced distribution of work allows a scalable network based on high-speed point-to-point links to be used for communicating between the pipelines. Pomegranate provides one interface per pipeline for issuing ordered, immediate-mode rendering commands and supports a parallel API that allows multiprocessor applications to exactly order drawing commands from each interface. A detailed hardware simulation demonstrates performance on next-generation workloads. Pomegranate operates at 87–99% parallel efficiency with 64 pipelines, for a simulated performance of up to 1.10 billion triangles per second and 21.9 billion pixels per second.

## Acknowledgements

I would like to thank my advisor, Pat Hanrahan, for his continual guidance. His advice has been invaluable, as has his patience with my forays into activities far removed from being a graduate student. I thank the other members of my reading committee, Bill Dally and Mark Horowitz, for their time and attention to detail. Bill Dally has provided a great engineering perspective that I have had the pleasure of being exposed to in multiple classes as well as personally. Mark Horowitz was a source of many insightful suggestions throughout my career at Stanford. I owe a large debt of gratitude to Kurt Akeley. I have had numerous enlightening discussions with him, and he has given me a deeper understanding of graphics architecture. Kurt's thoughtful comments on my thesis clarified not only my writing but also my ideas.

Stanford has been a wonderful place to go to school, in large part because of the people I had the good fortune to work with. In particular, Homan Igehy, Gordon Stoll, John Owens, Greg Humphreys and Ian Buck have all taught me a great deal. The certainty with which I argued with them all was nearly always because I was wrong. They, together with Jeff Solomon, Craig Kolb, Kekoa Proudfoot, Matt Pharr and many others have made being a graduate student very enjoyable.

The coincidences of my brother Adam attending graduate school at Stanford, David Rodriguez self-employing himself in Sunnyvale, and Michael and Tien-Ling Slater relocating to Berkeley have all made my time outside of school much more pleasurable.

I thank my parents for encouraging me to go to graduate school when I needed to be pushed, for their enthusiasm when I thought I would leave to go get rich, and for their constant encouragement to write my thesis when I was dragging my heels.

Finally, I thank the Fannie and John Hertz Foundation for its support, as well as DARPA contract DABT63-95-C-0085-P00006.

## **Contents**

| Al | Abstract |          |                                              |      |

|----|----------|----------|----------------------------------------------|------|

| A  | cknov    | vledgem  | nents                                        | vi   |

| 1  | Intr     | oductio  | n                                            | 1    |

|    | 1.1      | Graphi   | ics Pipeline                                 | . 2  |

|    | 1.2      | Perform  | mance Metrics                                | . 6  |

|    | 1.3      | Comm     | unication                                    | . 7  |

|    | 1.4      | Scalab   | ility                                        | . 8  |

|    | 1.5      | Summ     | ary of Original Contributions                | . 10 |

| 2  | Gra      | phics Pi | ipeline                                      | 13   |

|    | 2.1      | Choice   | es                                           | . 14 |

|    | 2.2      | Termir   | nology                                       | . 17 |

|    | 2.3      | Comm     | nunication Costs                             | . 18 |

|    | 2.4      | Paralle  | el Interface                                 | . 21 |

| 3  | Para     | allelism | and Communication                            | 24   |

|    | 3.1      | Paralle  | elism                                        | . 24 |

|    |          | 3.1.1    | Object Parallelism                           | . 27 |

|    |          | 3.1.2    | Image Parallelism                            | . 27 |

|    |          | 3.1.3    | Object Parallel to Image Parallel Transition | . 32 |

|    | 3.2      | Comm     | unication                                    | . 32 |

|    |          | 3.2.1    | Patterns                                     | . 34 |

|    |          | 3.2.2    | Networks                                     | . 35 |

|   |      | 3.2.3   | Memory                          | 38 |

|---|------|---------|---------------------------------|----|

| 4 | Taxo | onomy a | and Architectures               | 43 |

|   | 4.1  | Sort-F  | irst                            | 46 |

|   |      | 4.1.1   | Sort-First Retained-Mode        | 47 |

|   |      | 4.1.2   | Sort-First Immediate-Mode       | 48 |

|   | 4.2  | Sort-N  | Middle                          | 50 |

|   |      | 4.2.1   | Sort-Middle Interleaved         | 50 |

|   |      | 4.2.2   | Sort-Middle Tiled               | 50 |

|   | 4.3  | Sort-L  | ast Fragment                    | 55 |

|   | 4.4  | Sort-L  | ast Image Composition           | 56 |

|   |      | 4.4.1   | Pipelined Image Composition     | 57 |

|   |      | 4.4.2   | Non-Pipelined Image Composition | 60 |

|   | 4.5  | Hybrid  | d Architectures                 | 62 |

|   |      | 4.5.1   | WireGL + Lightning-2            | 63 |

|   |      | 4.5.2   | VC-1                            | 63 |

|   | 4.6  | Observ  | vations                         | 65 |

|   |      | 4.6.1   | Interface Limit                 | 65 |

|   |      | 4.6.2   | Application Visibility of Work  | 70 |

|   |      | 4.6.3   | Texturing                       | 71 |

|   |      | 4.6.4   | Limits of Image Parallelism     | 71 |

| 5 | Pom  | egrana  | te: Architecture                | 74 |

|   | 5.1  | Overv   | iew                             | 76 |

|   | 5.2  | Scalab  | oility and Interface            | 77 |

|   | 5.3  | Archit  | ecture                          | 79 |

|   |      | 5.3.1   | Network                         | 81 |

|   |      | 5.3.2   | Command Processor               | 82 |

|   |      | 5.3.3   | Geometry Processor              | 83 |

|   |      | 5.3.4   | Rasterizer                      | 85 |

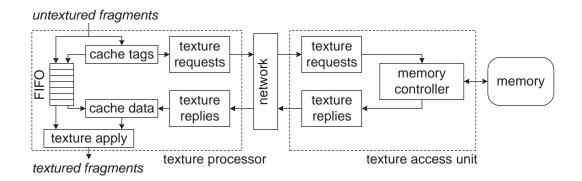

|   |      | 5.3.5   | Texture Processor               | 85 |

|   |      | 5.3.6   | Fragment Processor              | 88 |

|   |      | 537     | Dienlay                         | 20 |

| 6  | Pom   | negranate: Ordering and State | 91  |  |  |

|----|-------|-------------------------------|-----|--|--|

|    | 6.1   | Ordering                      | 91  |  |  |

|    |       | 6.1.1 Serial Ordering         | 92  |  |  |

|    |       | 6.1.2 Parallel Ordering       | 97  |  |  |

|    | 6.2   | State Management              | 103 |  |  |

|    |       | 6.2.1 State Commands          | 103 |  |  |

|    |       | 6.2.2 Context Switching       | 106 |  |  |

| 7  | Sim   | ulation and Results           | 108 |  |  |

|    | 7.1   | Scalability                   | 110 |  |  |

|    | 7.2   | Load Balance                  | 112 |  |  |

|    | 7.3   | Network Utilization           | 113 |  |  |

|    | 7.4   | Comparison                    | 114 |  |  |

| 8  | Disc  | eussion                       | 120 |  |  |

|    | 8.1   | OpenGL and the Parallel API   | 120 |  |  |

|    | 8.2   | Communication                 | 121 |  |  |

|    | 8.3   | .3 Consistency Model          |     |  |  |

|    | 8.4   | Shared State Management       | 123 |  |  |

|    |       | 8.4.1 Texture Objects         | 123 |  |  |

|    |       | 8.4.2 Display Lists           | 125 |  |  |

|    |       | 8.4.3 Virtual Memory          | 126 |  |  |

|    | 8.5   | Automatic Parallelization     | 127 |  |  |

|    | 8.6   | Pomegranate-2                 | 130 |  |  |

| 9  | Con   | clusions                      | 132 |  |  |

| Bi | bliog | raphy                         | 135 |  |  |

## **List of Tables**

| 2.1 | Communication cost between pipeline stages           |

|-----|------------------------------------------------------|

| 3.1 | Analysis Notation                                    |

| 3.2 | Interconnection Networks                             |

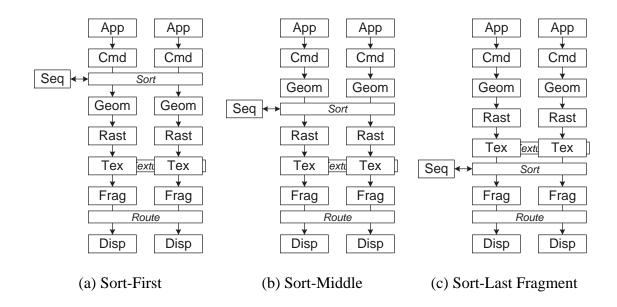

| 4.1 | Revised graphics taxonomy and alternative taxonomies |

| 4.2 | Summary of Graphics Architectures                    |

| 6.1 | Total FIFO sizes for each functional unit            |

| 6.2 | Context Size                                         |

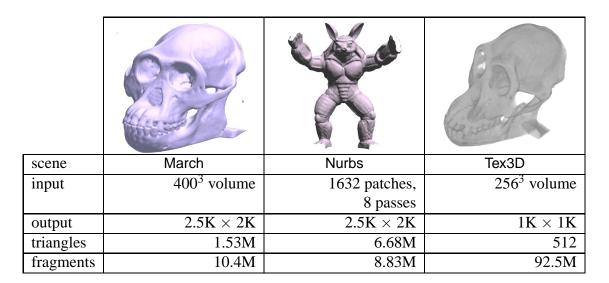

| 7.1 | Benchmark Scenes                                     |

| 7.2 | Load balance for Nurbs                               |

| 7.3 | Load balance for March                               |

| 7.4 | Load balance for Tex3D                               |

| 7.5 | Network traffic by type on a 64-pipeline Pomegranate |

## **List of Figures**

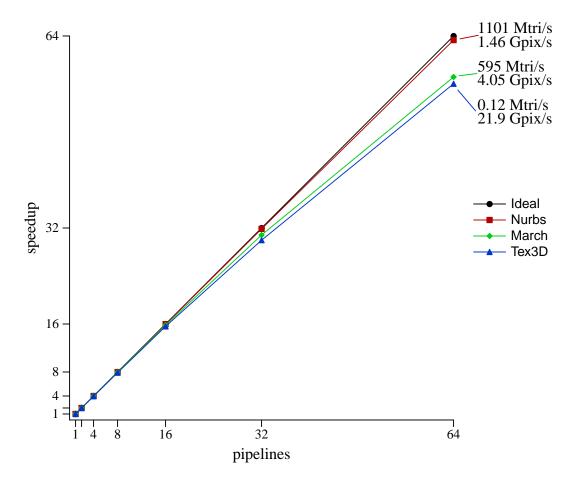

| 1.1  | Polygon Rendering Pipeline            | 2  |

|------|---------------------------------------|----|

| 1.2  | Parallel Graphics Performance Metrics | 6  |

| 2.1  | Graphics Pipeline Model               | 14 |

| 2.2  | Graphics Architecture Terminology     | 17 |

| 2.3  | Pipeline Communication Bandwidths     | 19 |

| 2.4  | Parallel API Example                  | 22 |

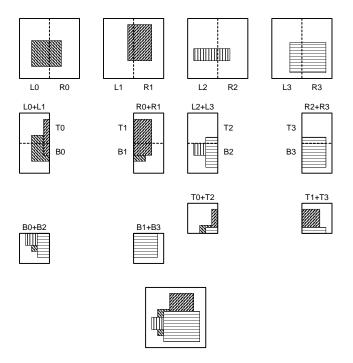

| 3.1  | Image Parallelism Choices             | 28 |

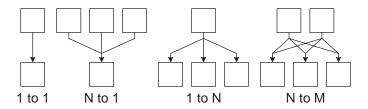

| 3.2  | Communication Patterns                | 34 |

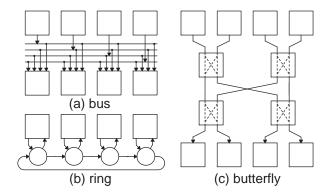

| 3.3  | Interconnects                         | 36 |

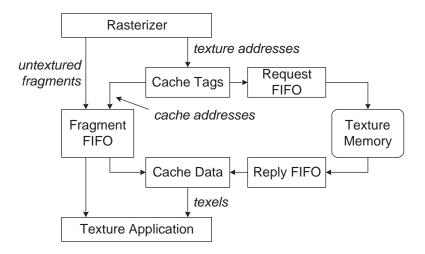

| 3.4  | Texture Prefetching                   | 39 |

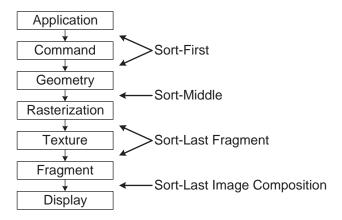

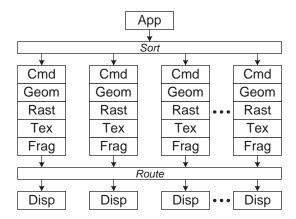

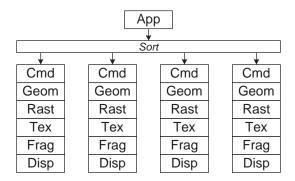

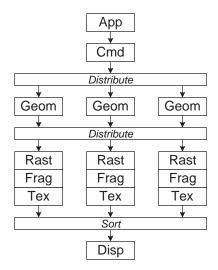

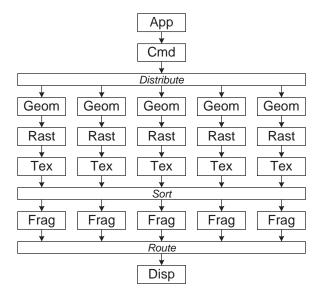

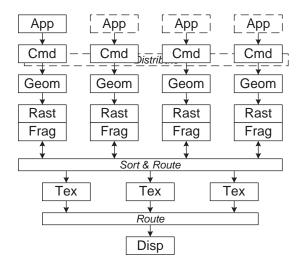

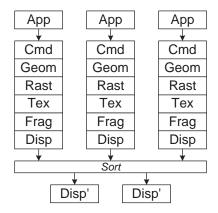

| 4.1  | Sorting Locations                     | 44 |

| 4.2  | Princeton Scalable Display Wall       | 47 |

| 4.3  | WireGL                                | 49 |

| 4.4  | SGI InfiniteReality                   | 51 |

| 4.5  | Argus                                 | 52 |

| 4.6  | UNC Pixel-Planes 5                    | 54 |

| 4.7  | Sort-Last Fragment                    | 55 |

| 4.8  | UNC PixelFlow                         | 58 |

| 4.9  | Lightning-2                           | 59 |

| 4.10 | Binary-Swap Compositing               | 60 |

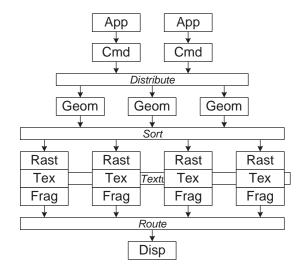

| 4.11 | WireGL and Lightning-2                | 62 |

| 4 12 | Aizu VC-1                             | 64 |

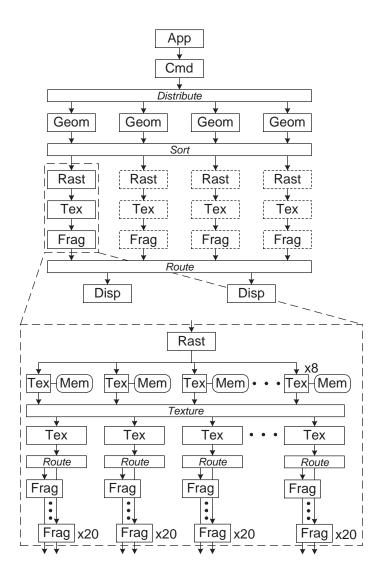

| 5.1 | Pomegranate Architecture                                            |

|-----|---------------------------------------------------------------------|

| 5.2 | Pomegranate pipeline                                                |

| 5.3 | Butterfly Network                                                   |

| 5.4 | Texture Stage                                                       |

| 5.5 | Texture Memory Organization                                         |

| 5.6 | Pixel Quad Memory Layout                                            |

| 5.7 | Framebuffer Tiling Patterns                                         |

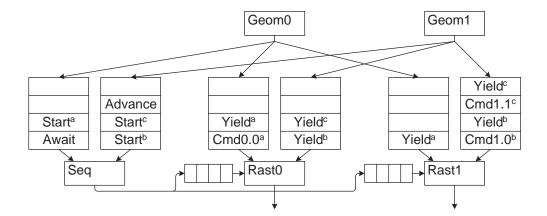

| 6.1 | Two Stage Communication Loses Serial Ordering                       |

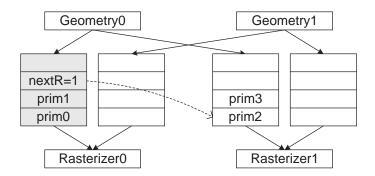

| 6.2 | NextR operation                                                     |

| 6.3 | NextR Operation (continued)                                         |

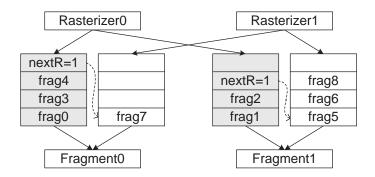

| 6.4 | Submit Threads                                                      |

| 6.5 | Example translation of a glBarrierExec into internal AdvanceContext |

|     | and AwaitContext operations                                         |

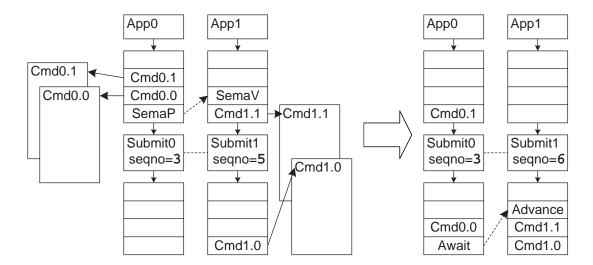

| 6.6 | Sequencer Operation                                                 |

| 6.7 | Communication of State Commands                                     |

| 7.1 | Pomegranate speedup vs. number of pipelines                         |

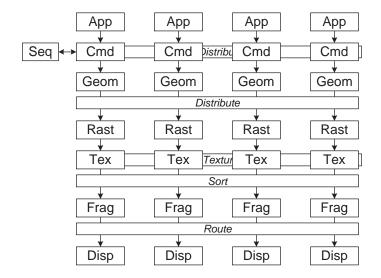

| 7.2 | Other architectures implemented on the Pomegranate simulator        |

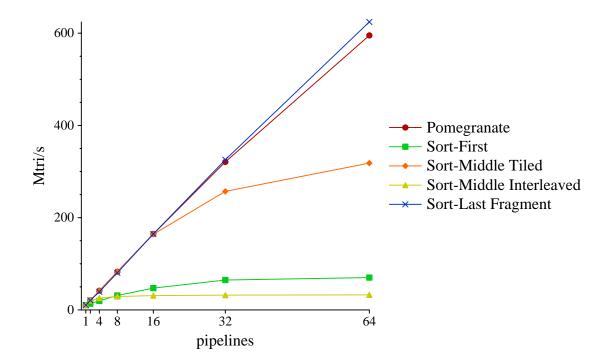

| 7.3 | March performance on all architectures                              |

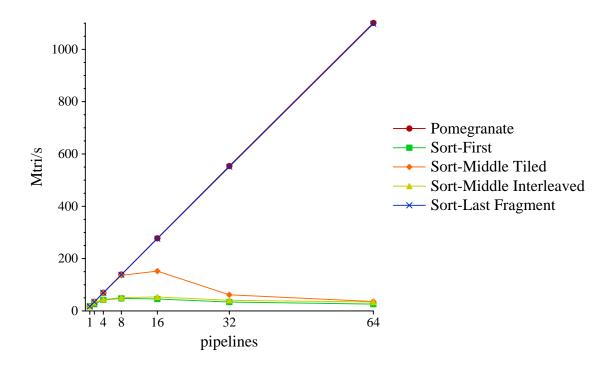

| 7.4 | Nurbs performance on all architectures                              |

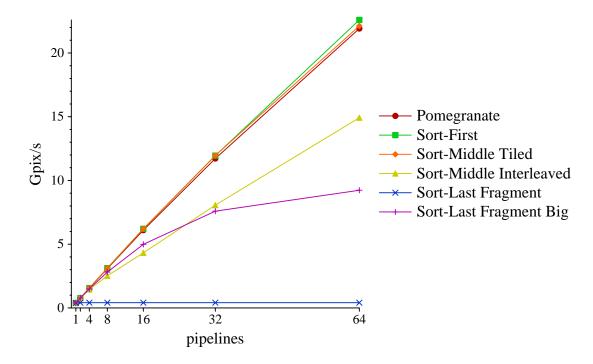

| 7.5 | Tex3D performance on all architectures                              |

| 8.1 | Pomegranate architecture, revised to share display lists            |

| 8.2 | Automatic Parallelization of Vertex Arrays                          |

| 8.3 | Automatic Parallelization of Display Lists                          |

| 84  | Pomegranate-2                                                       |

## **Chapter 1**

## Introduction

Scalability is a time machine. A scalable graphics architecture allows the combination of multiple graphics pipelines into a greater whole, attaining levels of performance that will be unattainable for years with a single pipeline. Parallel graphics addresses exactly those problems which exceed the capabilities of a single pipeline – problems such as scientific visualization, photorealistic rendering, virtual reality and large-scale displays. Once all of the available task parallelism has been exploited by providing dedicated hardware support for each stage of the pipeline, the path to increased performance is multiple pipelines, or data parallelism. The crucial element to exploiting data parallelism is communication.

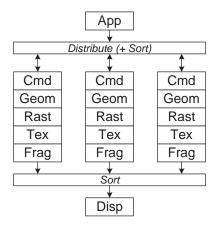

Graphics architectures are most broadly classified by where they "sort." The sort is the point in the architecture which transitions from object parallelism to image parallelism, and is literally the point where primitives are sorted by their screen location. The choice of where and how to perform this sort has an enormous impact on the resulting graphics architecture. Although the sort is generally the most visible form of communication in graphics architecture, communication takes place at other points in most architectures, with often significant ramifications. In part, this thesis presents an analysis of graphics architectures from a joint perspective of scalability and communication, examining their interdependence and discussing the results and limitations of different architecture choices.

We draw conclusions as to the main obstacles to building a scalable parallel graphics architecture, and use these observations as the foundation for a new, fully scalable, graphics architecture called "Pomegranate." In the second half of this thesis we describe Pomegranate's architecture and operation. Simulation results demonstrate Pomegranate's scalability

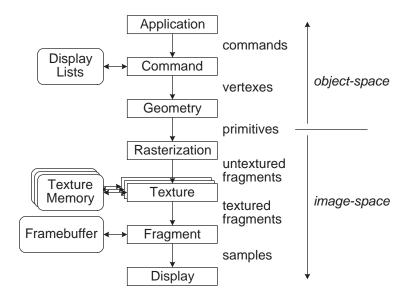

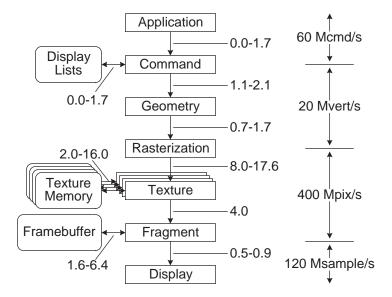

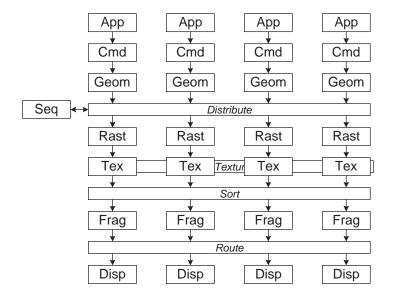

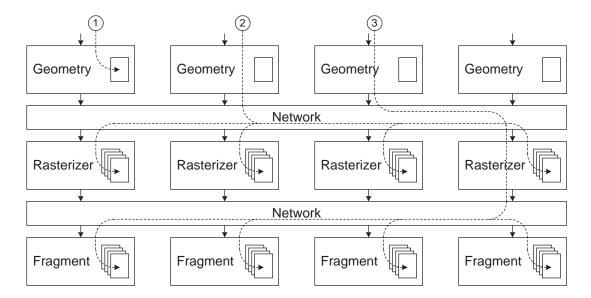

Figure 1.1: The Polygon Rendering Pipeline

to high degrees of parallelism.

We begin by describing the graphics pipeline and how we measure its performance. We then frame our discussion of communication and scalability in graphics architecture. Finally, we summarize the contributions of this thesis.

#### 1.1 Graphics Pipeline

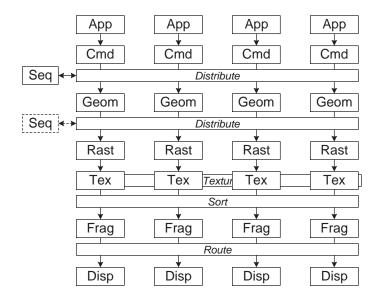

The polygon rendering pipeline, or graphics pipeline, takes as input commands that specify vertex positions, colors, geometric normals, texture coordinates, and other vertex attributes, and commands that specify the plane of projection, point of view, lighting model, etc., and computes as output an image of the polygons described by the input. The sequence of operations performed by the graphics pipeline is constant, but most operations may be configured by the application, and may be enabled or disabled as well. Our model of the graphics pipeline is shown in figure 1.1. The pipeline consists of seven stages: application, command, geometry, rasterization, texture, fragment and display. We have chosen the stages of the pipeline shown here both because they correspond well to our mental model of the operation of hardware, as well as clearly defining different points where communication

may be used.

The application generates the command stream that controls the graphics pipeline. These commands specify both the locations and various material and geometric attributes of polygon vertices, as well as setting the configuration of the pipeline. These commands are input to the command processor which manages the interface between the graphics system and the host processor.

The command processor provides the graphics pipeline's interface to the application. It accepts the application's vertex commands and tracks their effects on the graphics state. State that the application does not modify is persistent. For example, if the application sets the color to red, then every subsequent vertex will be red, until a new color specified. The command processor bundles each incoming vertex together with the tracked vertex attributes, and passes them to the geometry processor. The command processor additionally interprets display lists, which are execution macros for a number of graphics commands. The use of display lists avoids the the specification of the same commands multiple times, reducing application computation, and the lists may be stored in graphics memory, reducing interface bandwidth.

The geometry processor transforms the application specified vertices, which exist in their own local coordinate system, by application specified transformation matrices, mapping the vertices to their screen locations. The geometry processor similarly transforms the vertex geometric normals, and evaluates a lighting model. The transformed vertices are then assembled into primitives, which may be culled if they do not lie on the screen, or clipped to the boundary of the screen if they intersect it. The resulting screen-space primitives are then sent to the rasterizer.

The rasterizer receives primitives, which are specified by the location, color and texture coordinates of their vertices on the screen. The rasterizer emits a fragment for every pixel location a primitive overlaps. Each fragment includes pixel coordinates, color, depth, and texture coordinates, interpolated from the primitive's vertices.

The texture processor textures the stream of fragments from the rasterizer. For each fragment it retrieves a texel neighborhood from the current texture and filters the texels to compute a final texture color, which is then combined with the fragment's color. The application specifies the texture images which are used by the texture processor. Modern

graphics pipelines may include multiple texture processors, with the output color of each texture processor taken as the input color to the next. In this case the rasterizer interpolates independent texture coordinates for each texture processor.

The fragment processor accepts the stream of texture fragments from the last texture processor, and combines it with the framebuffer. Typically the fragment processor composites the fragments according to the results of a depth test, updating the color stored in the framebuffer only if the incoming fragment is closer to the eye than the sample already in the framebuffer. The fragment processor may be configured to perform a number of additional operations, such as blending the incoming fragment color with the color already present in the framebuffer.

The display processor continually reads the contents of the framebuffer and sends it to the display.

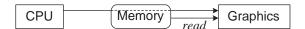

The command processor, texture processors and the fragment processor in our pipeline are connected to memory systems. The command processor may have direct access to a local memory system to store display lists or other retained-mode constructs, without having to use the application's memory system resources. Similarly, the texture processors in most modern systems have a locally attached memory system for high-bandwidth access to the texture store. Finally, the fragment processor is attached to the framebuffer. Here the representation of distinct memory for each task is schematic, in many modern architectures there is a single unified memory system that satisfies all of these uses.

The pipeline in figure 1.1 is annotated with what is communicated between each of its stages. Although not labeled separately, the memory provides communication as well. Instead of providing communication in space, by connecting separate functional units, memory provides communication in time, allowing data computed or specified at one time to be used at a later time. We discuss the cost of communication in both interconnect and memory in section 2.3.

The transition from communication of object-space primitives and commands to screenspace primitives and commands is mirrored in the use of parallelism within the graphics pipeline. All parallel graphics architectures will initially exploit object parallelism, at least at the level of processing the input command stream, and in the end will exploit image parallelism when driving the display. However, the transition from object-space primitives to screen-space primitives does not dictate where the transition from object parallelism to image parallelism must occur. Section 3.1 discusses the use of object-space and screen-space parallelism in the graphics pipeline.

The pipeline we have just described has a stateful immediate-mode interface and ordered semantics. There are other choices that could have been made, and in section 2.1 we discuss the implications of these choices and their alternatives, both for application programmers and hardware architects.

In a conventional microprocessor pipeline, each instruction accepts a fixed number of inputs, typically two, and computes a constant number of outputs, typically just one. In contrast, the computation in a graphics pipeline is much more variable. A single triangle may be located outside of the viewing frustum, in which case it requires little computation, and its processing ceases during the geometry stage of the pipeline, or a triangle may cover the entire screen, in which case the rasterization and subsequent stages of the pipeline will spend a proportionally large amount of time processing it. Generally neither the location nor the area of a primitive on the screen is known a priori, and by extension, neither is the amount of computation required to process the primitive.

The dynamic amount of processing required for each primitive presents the fundamental challenge to exploiting data parallelism in a graphics architecture. Although geometric processing imbalances can be significant, the primary difficulty is the widely varying amount of rasterization processing required per primitive. In broad strokes, there are two approaches to addressing this problem in data parallel graphics. The first, more commonly used approach, is to partition the output space (screen) across the rasterizers. Thus large primitives will be processed by many pipelines, and small primitives by just a single pipeline. The primary difficulty to these *image parallel* schemes is choosing a partition that achieves a good load balance without excessive duplication of work. The second approach is to partition the input space (primitives) across the rasterizers. Architectures based on this approach typically assume that, given a sufficiently large number of primitives, each pipeline will have a balanced amount of work. The main challenge of such *object parallel* approaches is that this is in fact a poor assumption. We discuss these approaches to parallelism, and the communication they require, in chapter 3. In chapter 4 we present an extended taxonomy of architectures, and discuss examples of each.

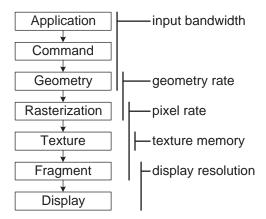

**Figure 1.2**: Parallel Graphics Performance Metrics. Each of the performance metrics will be governed by the stages indicated as well as any communication between the stages.

#### 1.2 Performance Metrics

We identify five key performance metrics, shown in figure 1.2, for evaluating a parallel graphics architecture: input bandwidth, geometry rate, pixel rate, texture memory and display resolution.

Input bandwidth is the rate at which the application can generate commands, pass them to the command processor and have them accepted by the geometry processor. In this case, it is assumed that the limiting factor is command submission and that the primitives are small and simple enough to be neither geometry nor pixel rate limited.

Geometry rate is the rate at which the geometry processor can transform, light and clip input primitives and transmit the results to the rasterizer. Recent geometry processors are fast enough that they are often limited by input bandwidth for immediate-mode applications, unless they are performing complicated lighting or texture coordinate generation.

Pixel rate is the rate at which the rasterizer can accept primitives, scan convert them, and emit fragments. The pixel rate is similarly dependent on the rate at which the texture processor can texture the fragments and the fragment processor can merge the fragments with the framebuffer.

Texture memory is the amount of memory available for unique textures. If an architecture replicates texture memory, for example, providing a complete copy of all textures

for each texture processor, then the unique texture memory is the total amount of texture memory divided by the replication factor.

Display resolution is the resolution and number of displays which can be supported.

Each of these performance metrics is determined not only be the compute and memory capacity of its particular stages, but also by the communication mechanisms which connect those stages.

#### 1.3 Communication

Communication forms the backbone of parallel graphics, allowing multiple functional units to cooperate to render images. How various architectures use communication to distribute the parallel computation will be our be primary means of differentiating them. Communication serves two main purposes within parallel graphics. First, it enables the *fan-out* and *fan-in* of parallel computations. Nearly all parallel graphics architectures fan-in parallel computation at the display – communication is used to route the parallel computation of the frame by multiple pipelines to a display or displays. Most architectures additionally use communication to fan-out an input serial command stream, distributing its work over the pipelines. The second purpose of communication is to garner *efficiency*. Communication helps us garner efficiency by allowing us to load-balance work across pipelines and reduce duplication of memory and computation.

Communication allows us to balance the computational load across the various pipelines so that the pipelines are uniformly utilized. Load-balancing is necessary because even if the same number of primitives is given to every pipeline, those primitives will differ both in the amount of geometric work required and the amount of rasterization work required. Given that the amount of work required per primitive is generally not known a priori, the work may either be distributed dynamically, relying on work estimators and feedback to balance the load, or statically, relying on a statistical load balance. We will see that in practice load-balanced static partitions are quite difficult to implement efficiently.

Communication allows us to reduce duplication of memory by, for example, partitioning the framebuffer among the pipelines and sorting work to the appropriate pipeline, rather

than providing a duplicate framebuffer for each pipeline. Similarly, we may choose to partition the texture memory among the pipelines in the system and communicate texture reads between pipelines rather than replicating the texture store on each pipeline. In the same vein, communication allows us to perform a computation once and communicate the result to all the necessary recipients, rather than having them each perform the computation. For example, communication between geometry and rasterization allows each primitive to be transformed and setup only once, although multiple rasterizers may be responsible for the computation of its fragments.

Rather than using communication to reduce duplication of memory, we can use memory to reduce communication. For example, it may be more efficient to replicate texture memory on each pipeline, rather than sharing it over a texture memory interconnect. Similarly, the application might put its commands into display lists which can be cached in the graphics system, so the commands do not utilize the scarce host interface bandwidth, or the host's scarce compute cycles. In effect, memory provides communication across time, allowing the architecture to use computations (textures, commands, etc.) at a time deferred from their specification.

We take a unified view of both interconnect and memory as communication. An interconnect provides communication across space, while a memory provides communication across time. In part, we analyze the differences in these forms of communication, and show how they may be interchanged.

#### 1.4 Scalability

The performance of interactive graphics architectures has been improving at phenomenal rates over the past few decades. Not only have the speed improvements kept up with or exceeded Moore's Law, but each successive generation of graphics architecture has expanded the feature set. Despite these great improvements, many applications cannot run at interactive rates on modern hardware. Examples include scientific visualization of large data sets, photo-realistic rendering, low-latency virtual reality, and large-scale display systems. A primary goal in graphics research is finding ways to push this performance envelope, from the details of the chip architecture to the overall system architecture.

The past few years have also marked a turning point in the history of computer graphics. Two decades ago, interactive 3D graphics systems were found only at large institutions. As semiconductor technologies improved, graphics architects found innovative ways to place more functionality on fewer chips, and interactive graphics workstations made their way to the desktops of engineers. Today, the entire graphics pipeline can be placed on a single chip and sold at a mass-market price point. Because of the enormous economies of scale afforded by commodity parts, this trend has a significant impact on how high-end systems must be built: it is much more cost effective to design a single low-end, high-volume system and replicate it in an efficient manner in order to create high-end, low-volume systems. For example, supercomputers used to be designed with unique, proprietary architectures and esoteric technologies. As microprocessors became commodity parts, these designs were replaced by highly parallel multiprocessor systems that made use of microprocessor technology.

In this thesis we examine graphics architectures from a perspective of scalability. We consider not only how well a particular implementation of an architecture works, but also how that architecture's performance scales with increasing parallelism. From our observations of existing architectures, we synthesize a new architecture, called "Pomegranate." The Pomegranate architecture, described in chapter 5, provides a way of scaling the base unit of a single graphics pipeline to create higher performance systems, with near linear performance increases in all of our graphics performance metrics.

In many fields, parallelism is employed not to solve the same problem faster, but instead to solve a bigger problem at the same speed. This is particularly true of interactive computer graphics. Humans interact well at frame rates between approximately 100Hz and 1Hz. Above 100Hz the improved performance is not perceivable, and below 1Hz the system loses interactivity. Thus, parallel graphics is generally used to visualize bigger problems, rather than the same problems faster.

This has a profound effect on how parallelism is managed. If we expect a system that is twice as large to be used to render scenes that are twice as large, then approaches which perform broadcast communication proportional to the size of the input, either over interconnects or by replicating memory, have a cost that grows as  $O(n^2)$  – each of n units will require communication that scales as n. In order to be a truly scalable graphics architecture,

Pomegranate was specifically designed to avoid the use of broadcast communication, and in chapter 7 we demonstrate its efficiency, and compare its performance to other graphics architectures.

#### 1.5 Summary of Original Contributions

The original contributions of this work are in two areas. First, we present an analysis of parallel graphics architecture based on communication:

- Extended Taxonomy We present a detailed discussion of the types of communication used in parallel graphics. We distinguish four kinds of communication: sorting, which connects object and image parallel stages, distribution, which connects object parallel stages, routing, which connects image parallel stages, and texturing, which connects untextured fragments with texture samples. We show that while sorting has been the traditional focus of parallel graphics architecture, distribution, routing and texturing are just as critical. This motivates our introduction of an extended taxonomy of parallel graphics architecture. Our taxonomy more accurately describes the location of the sort, in particular distinguishing architecture which sort fragments from those which composite images. We analyze several hardware and software graphics architectures under our taxonomy, focusing on their use of communication and parallelism, and the resulting ramifications on the architecture's scalability.

- Insight to Limitations We analyze the limitations of the architectures described under our taxonomy. We discuss the importance of the application visibility of work, so that the efficiency of the graphics system will depend only on application visible characteristics of the input. We consider the limitations of image parallelism, and argue that deferring image parallelism until fragment processing has strong advantages. We examine approaches to solving the limitations of a serial interface and conclude that for many applications a parallel interface is the only appropriate solution. Finally, we discuss the impact of efficiently supporting texturing, and conclude that object-parallel or coarse granularity image parallelism should be used.

Then we present Pomegranate, a new, fully scalable, graphics architecture. We originally described Pomegranate in [Eldridge et al., 2000], the description here is significantly expanded:

- **Designed for Communication Efficiency** Pomegranate's parallelism is chosen to not require the use of broadcast communication, but only general all-to-all communication. As a result, Pomegranate requires total interconnect bandwidth proportional to the number of pipelines. We demonstrate the achieved efficiency of Pomegranate's communication scheme, and discuss ways to address imbalances at high degrees of parallelism.

- Scalable in All Performance Metrics Pomegranate provides scalable input bandwidth, geometry rate, pixel rate, texture memory, and display bandwidth. Pomegranate is the first parallel graphics architecture to offer scalability in all these metrics. We show how the structure of Pomegranate's parallelism insures this scalability, and we present simulation results to validate our claims.

- Support for Parallel Input We support a parallel interface to the hardware that allows multiple applications to submit commands simultaneously and independently to the hardware. Familiar parallel programming primitives extend the API and express ordering constraints between the execution of these commands. We demonstrate the efficiency of Pomegranate's parallel interface with parallel applications that submit work with both partial and total orders.

- Novel Ordering Mechanisms We describe novel ordering mechanisms that we use to provide support for the ordered semantics of a serial command stream, and for the correct interleaving of multiple command streams under our parallel interface. We discuss the efficiency of this approach, as well as its ultimate performance limitations, which are reflected in a minimum granularity parallel work, and eventual communication limitations at high degrees of parallelism. We consider utilizing a dedicated communication mechanism as a possible solution to the second problem.

- **Simulated Performance to 64 Pipelines** We have constructed a detailed simulation of the Pomegranate architecture. We simulate Pomegranate's performance on three

12

different applications, from 1 to 64 pipelines. We demonstrate excellent scalability, with 87% to 99% parallel efficiency on 64-pipeline systems.

• Comparison to Other Architectures By restructuring the Pomegranate simulator, we compare Pomegranate's performance to sort-first, sort-middle, and sort-last architectures. We find performance problems for each of these architectures on different applications. We examine the causes of the observed performance, and discuss how Pomegranate addresses these problems to obtain scalable performance.

We conclude by discussing design choices made in the Pomegranate architecture, and speculating on what choices might be appropriate in the future.

## Chapter 2

## **Graphics Pipeline**

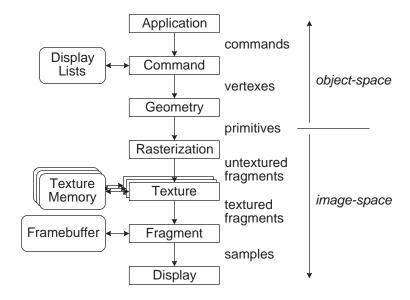

The graphics pipeline described in the introduction is an OpenGL-style pipeline. We repeat the pipeline diagram in figure 2.1. A more detailed description of the OpenGL pipeline can be found in the OpenGL Reference Manual [OpenGL Architecture Review Board, 1997] and the OpenGL specification [Segal and Akeley, 1999]. We now discuss our motivation for choosing an OpenGL pipeline model, and the alternative choices that could have been made. We will also define our choice of terminology for describing graphics architectures. Given our pipeline model, we provide a detailed accounting of the cost of communication within the pipeline, and explain our extension of the graphics pipeline to accommodate a parallel interface.

We present a baseline set of graphics pipeline functionality in this work, but our discussion and analyses do not preclude extensions and changes to the pipeline. For example, some current graphics pipelines, and likely more pipelines in the future, include support in the geometry processor for tessellation of input primitives. While this will change some specific details of the pipeline operation – for example, it will affect the ratio of input bandwidth to the number of rasterization primitives – our fundamental analysis of graphics architectures remains the same.

Figure 2.1: Graphics Pipeline Model

#### 2.1 Choices

From an implementation point of view, the OpenGL pipeline is a long sequence of operations, with associated pieces of state that control the operation of various stages. For example, the API call glBlendFunc controls how fragments are combined with the framebuffer. As commands are submitted to the hardware, via the OpenGL API, they are executed more or less immediately, without, for example, waiting for an explicit command to cause the scene to be rendered. OpenGL specifies ordered semantics, analogous to those found in most pipelined microprocessor pipelines. Despite any internal use of parallelism to accelerate its computations, the hardware always appears to execute all commands in the order specified by the application.

This thesis is based on an OpenGL-style pipeline, which specifies a stateful immediatemode interface with ordered semantics. Although OpenGL has made these particular choices, other decisions could have been made. Other options are discussed next.

The graphics interface may either be immediate-mode or retained-mode. An immediate-mode interface allows the application to specify commands directly to the pipeline which are then rendered, more or less immediately. Such an interface provides the greatest flexibility for the application, and readily supports time-varying and dynamic content. A

retained-mode interface builds an internal representation of the scene, which is then traversed to generate the output image. Extensive facilities may be provided to allow the application to edit this retained representation. Retained-mode interfaces are typically used to attain performance higher than that which is possible through an immediate-mode interface (due to application limited submission bandwidth) or to avoid addressing the complexities of an immediate-mode interface. Immediate-mode interfaces may also support retained-mode constructs, for convenience and potentially for improved performance. OpenGL supports a retained-mode within its immediate-mode interface via display lists.

A stateful interface has the semantics of a persistent pipeline configuration, which is modified via API calls. A stateless interface bundles the pipeline configuration with each primitive or batch of primitives. The advantage of a stateless interface is that different batches of primitives may be processed independently, as there can be no dependencies between them, except for their effects on the framebuffer. Stateful interfaces have the disadvantage that they may limit the available parallelism, by requiring that the entire command stream be observed to know the value of any particular piece of the state. The advantage of a stateful interface is that the configuration of the pipeline need only be communicated when it is changed, rather than with each batch of primitives. The distinction we have drawn is at the interface, but similar choices may be made within the hardware itself. For example, many software rendering systems maintain a stateful interface for programmer convenience, but internally operate in a stateless fashion, to avoid the difficulties of dealing with state maintenance. Typically immediate-mode interfaces are stateful, as it provides a natural programming model and can greatly lessen the interface bandwidth to the pipeline. Retained-mode interfaces may be either stateful or not.

Ordered semantics have the same meaning for a graphics pipeline as they do for conventional processing: commands appear to execute in the order specified. However, the order of execution of a command is only visible via its effects on the state. Thus the pipeline is free to execute commands in any order, as long as the observed state of the system is the same as if the commands had been performed in exactly the order specified.

There are three main pieces of state in the graphics pipeline: the framebuffer, the texture

<sup>&</sup>lt;sup>1</sup>In section 8.5 we will discuss vertex arrays, which specifically relax this requirement to allow higher performance implementations.

memory, and the pipeline configuration. The framebuffer is probably the most challenging piece of state to manage.<sup>2</sup> A great deal of parallel graphics architecture has dealt with how to provide parallel access to the framebuffer in a load-balanced fashion, while maintaining semantics desirable to the programmer. Texture memory, although generally larger than the framebuffer, is usually an easier management problem because it is largely read-only, and thus the ordering problems which plague the framebuffer may be avoided by taking some care when textures are modified. Pipeline configuration is the final piece of state to manage. Assuming that the architects have gone to the trouble to support ordering at the framebuffer, which falls at the end of the pipeline, then ordering the commands which modify the pipeline configuration leading up to the framebuffer is straightforward. The same mechanism that maintains the ordering of primitives until the framebuffer can be reused to order the configuration commands. In fact, when these configuration commands are not ordered by the same mechanism, but are instead executed via a sideband path, it is typically a source of lost performance, because the pipeline must be flushed before the commands can be executed.

When ordering is not fully supported it has typically been relaxed or eliminated at the framebuffer, removing the guarantee that fragments are composited in the order their corresponding primitives were submitted. While this relaxation may be acceptable for depth-composited rendering, it practically eliminates the possibility of supporting transparency, and other techniques which rely on program controlled compositing order. Note that the ordering requirements at the framebuffer are in fact fairly relaxed already. In particular, order is only visible on a pixel-by-pixel basis. Thus an architecture with many image parallel fragment processors need not coordinate the processors in general – as long as each does its work in order, the overall set of work is done in order.

Systems with a stateless interface, or those that are stateless internally, may further relax ordering. Such systems can carry the pipeline and texture configuration along with each batch of primitives, and thus batches of primitives can be readily reordered. IRIS Performer, a scene graph library built on top of OpenGL, specifically disallows particular

<sup>&</sup>lt;sup>2</sup>Interestingly, the OpenGL graphics system specification [Segal and Akeley, 1999] describes operations that are performed on the framebuffer, but the framebuffer is not actually part of the graphics state. Unlike texture and the pipeline configuration, the framebuffer is always shared among all of the graphics contexts, and is thus part of the window system state.

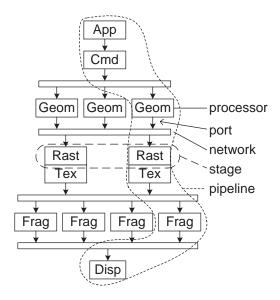

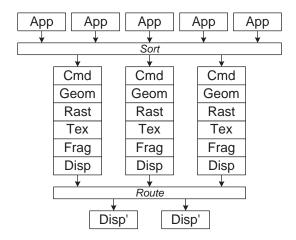

**Figure 2.2**: A parallel graphics architecture is composed of multiple *pipelines*, each of which is made up of a sequence of *processors*. A horizontal slice across all the pipelines containing all of the instances of a given unit makes up a *stage*. General communication occurs over *networks*, shown as rectangles, and each unit interfaces with the network via a *port*.

forms of state inheritance, which allows them to perform many optimizations when rendering the scene [Rohlf and Helman, 1994]. For example, entire subgraphs may be culled if they are outside of the viewing frustum, and no energy needs to be spent examining the effects of the culled nodes on the state, because by definition they cannot have any effect.<sup>3</sup> Similarly, Performer may sort all of the geometry to be rendered by state configuration, thus minimizing the number of potentially expensive configuration changes in the hardware.

#### 2.2 Terminology

The terminology we will use to describe the parts of a parallel graphics architecture, as well as our style of drawing these architectures, is defined in figure 2.2. The graphics pipeline is made up of a sequence of functional blocks, referred to abstractly as *processors*. A set of identical processors, e.g. all of the rasterizers, are collectively referred to as a *stage*.

<sup>&</sup>lt;sup>3</sup>Technically, a node in the scene graph saves all of the state it will modify, and restores the state after its execution. Thus state is inherited top-down, but not left-to-right.

We refer to a set of processors that together would form a serial graphics pipeline as a *pipeline*, recognizing that the actual architecture may not consist of simple replications of this pipeline. For example, there may be twice as many fragment processors as there are rasterizers. The stages of the architecture can be interconnected in many ways, which we represent schematically. If two units only communicate with each other, and are located in the same package, they are abutted to show this relationship. For example, the rasterizers and texture processors are paired in the fictitious architecture in figure 2.2. If the two units of a pair are connected by external communication this is shown by an arrow between them, as in the application and command processors which are connected by the host I/O subsystem. Shared communication mechanisms, connecting one or more sources to one or more sinks, are depicted as rectangles. We refer to such shared mechanisms as *networks* and each source and sink has a *port* in to or out of the network.

#### 2.3 Communication Costs

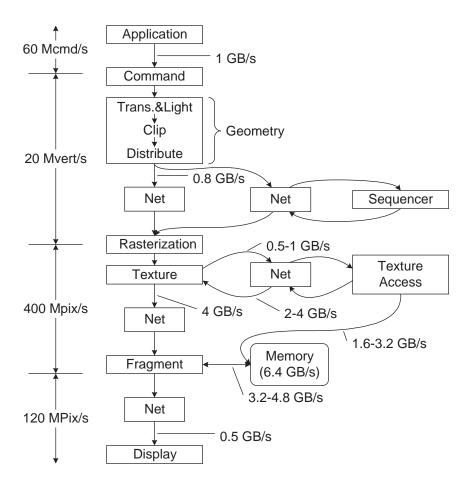

Given our graphics pipeline model, we can now examine the cost of communication at various points in the pipeline. Figure 2.3 summarizes the bandwidth required for a modern graphics pipeline operating at 20 Mvert/sec and 400 Mpixel/sec. A detailed counting of the data communicated in the pipeline is provided in table 2.3. Most architectures will not use communication at all these points in the pipeline. For example, the rasterizer and texture processor may be coupled, in which case untextured fragments are passed internally between the units.

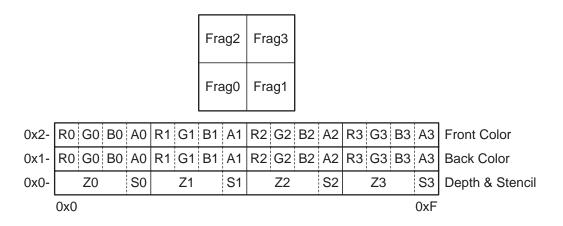

The cost of communication presented here is representative, and may be less (or more) in practice. Texture reads are often blocked, for example a  $4 \times 4$  texel read, which amortizes the cost of the texture address down to a few bits per texel. When communicating textured or untextured fragments it is common to send a small stamp of fragments, for example a  $2 \times 2$  fragment quad, reducing the overhead of encoding position and allowing depth to be encoded more compactly as the z of one fragment and z slopes in x and y. Sample masks readily extend such a fragment-encoding scheme to efficiently transmitting super-sampled fragments.

Although we have not yet discussed parallelism, we can already draw some conclusions

**Figure 2.3**: Communication bandwidths in gigabytes per second for a 20 Mvert/sec, 400 Mpixel/sec graphics pipeline with a  $1600 \times 1200$  display. Input bandwidth from the application may be traded off against internal bandwidth from display list memory. The texture memory bandwidth assumes a read of 2 texels per fragment per active texture, 16 or 32-bit textures, and 1 to 4 active textures. The framebuffer memory bandwidth assumes a best case of a depth read and reject, and a worst case of reading and writing depth and color.

about the use of communication. For example, communication before geometry processing, as typified by a sort-first architecture, is comparable in expense to communication between geometry and rasterization, as in a sort-middle architecture. Furthermore, assuming the trend of increasing per-fragment complexity continues (multiple textures, per-fragment lighting, etc.) then the cost of communicating fragments between rasterization and texturing can become quite high, while the cost of communicating fragments after texturing remains relatively fixed.

It is interesting to note that as primitives become smaller and have more parameters (multiple texture coordinates, separate diffuse and specular color, etc.) the cost of communicating textured fragments becomes more and more favorable when compared to communicating primitives, and at approximately 8 pixel triangles they are equal. Thus, in the future, fragment-sorting architectures may be preferable to geometry-sorting architectures

|                  |                                | precision | bits    |

|------------------|--------------------------------|-----------|---------|

| Commands         |                                |           |         |

| glVertex3f       | <i>x</i> , <i>y</i> , <i>z</i> | 32        | 96      |

| glColor4f        | r, g, b, a                     | 32        | 128     |

| glNormal3f       | $n_x$ , $n_y$ , $n_z$          | 32        | 96      |

| glTexCoord2f     |                                | 32        | 64      |

| glMultiTex-      |                                |           |         |

| Coord2f (0-3)    | tex, s, t                      | 32        | 0-288   |

| total            |                                |           | 384-672 |

| Vertexes         |                                |           |         |

| position         | <i>x</i> , <i>y</i> , <i>z</i> | 32        | 96      |

| color            | r, g, b, a                     | 32        | 128     |

| normal           | $n_x$ , $n_y$ , $n_z$          | 32        | 96      |

| texture (1-4)    | s, t, r, q                     | 32        | 128-512 |

| total            |                                |           | 448-832 |

| Primitives       |                                |           |         |

| position         | <i>x</i> , <i>y</i>            | 16        | 32      |

| depth            | z, w                           | 32        | 64      |

| color            | r, g, b, a                     | 16        | 64      |

| texture (1-4)    | s, t, r, q                     | 32        | 128-512 |

| total            |                                |           | 288-672 |

| Untextured Fragm | ents                           |           |         |

| position         | <i>x</i> , <i>y</i>            | 12        | 24      |

| depth            | $\mathcal{Z}$                  | 24        | 24      |

| color            | r, g, b, a                     | 12        | 48      |

| texture (1-4)    | s, t, r, q                     | 16        | 64-256  |

| total            |                                |           | 160-352 |

| Texels           |                                |           |         |

| address          | a                              | 24-32     | 24-32   |

| color            | r, g, b, a                     | 4-8       | 16-32   |

| total            |                                |           | 40-64   |

Table 2.1: Communication cost between pipeline stages. (cont.)

|                    | precision | bits  |

|--------------------|-----------|-------|

| Textured Fragments |           |       |

| position $x, y$    | 12        | 24    |

| depth z            | 24        | 24    |

| color $r, g, b, a$ | 8         | 32    |

| total              |           | 80    |

| Samples            |           |       |

| color $r, g, b$    | 8         | 24    |

| depth z            | 0-24      | 0-24  |

| total              |           | 36-60 |

**Table 2.1**: Communication cost between pipeline stages. Commands are either written to DMA buffers and prefixed with opcodes, or in some cases written directly to the hardware, with the opcode implicit in the address of the write. Vertices are passed between the command processor and geometry unit, and may be fully expanded, encoding all the vertex properties, or may be passed along incrementally, only transmitting those attributes which have changed since the last vertex. The geometry unit transmits primitives to the rasterization units, and may take advantage of meshing information and send only the new vertices for each primitive, or may send each primitive independently. The rasterizer sends untextured fragments to the texture processor, which then emits textured fragments to the fragment processor. Finally the fragment processor sends samples to the display processor, which include no x, y position information because the information is typically implicit, as the fragments are sent in raster order, although z would be included in a depth-compositing architecture.

purely from a bandwidth perspective. We will show later that there are good reasons to prefer fragment sorting to geometry sorting, even at the cost of increased communication bandwidth.

#### 2.4 Parallel Interface

While building internally parallel graphics hardware is challenging in its own right, modern graphics accelerators often outstrip the ability of the host interface to supply them with data. Igehy, Stoll and Hanrahan introduced a parallel API for graphics to address this bandwidth limitation [Igehy et al., 1998b]. The parallel API extends OpenGL with synchronization primitives that express ordering relationships between two or more graphics contexts that

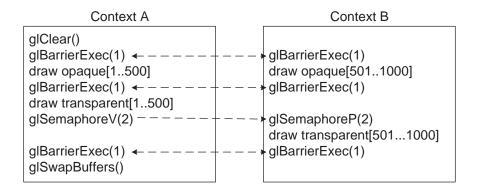

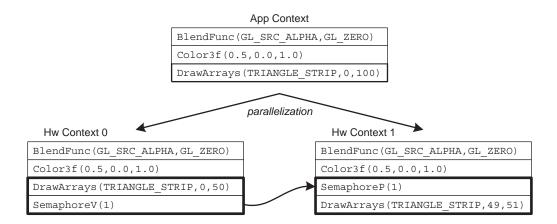

**Figure 2.4**: Parallel API Example. The scene to be rendered consists of 1000 opaque primitives and 1000 transparent primitives. The opaque primitives are rendered with depth compositing enabled, and the transparent primitives are rendered in back to front order. The pseudocode uses two contexts to submit this scene in parallel. The first barrier ensures that the clear performed by context A is complete before context B starts drawing. The second barrier ensures that all the opaque primitives are drawn before any transparent primitives. The semaphore pair ensures that context A's half of the transparent primitives are drawn first. The final barrier ensures that all drawing is done before the swapbuffers occurs.

simultaneously submit commands to the hardware. The significance of these primitives is that they do not execute at the application level, which allows the application threads to execute past the synchronization primitives and continue submitting work. These synchronization commands are then later executed by the graphics system. This allows the programmer to order the execution of the various contexts without being reduced to using a serial interface. The primitives we focus our attention on are barriers and semaphores.

A barrier synchronizes the execution of multiple graphics contexts, ensuring that all of the commands executed by any of the contexts previous to the barrier have completed before any of the commands subsequent to the barrier have any effect. A barrier is defined with glBarrierCreate (name, count), which associates a graphics barrier that has count contexts participating in it with name. A graphics context enters a barrier by calling glBarrierExec (name). A semaphore provides a point-to-point ordering constraint, and acts as a shared counter. A semaphore "V" (or up) operation atomically increments the counter. A semaphore is defined with zero, and then atomically decrements the counter. A semaphore is defined with

23

glSemaphoreCreate (name, initialCount), V'd by glSemaphoreV (name) and P'd by glSemaphoreP (name). Figure 2.4 provides an example of the use of these primitives.

## **Chapter 3**

## **Parallelism and Communication**

Parallelism and communication are intimately connected. Communication allows us to merge the parallel computation of an image to generate a display, as well as to split a serial input to process it in parallel. We will first discuss the forms of parallelism available in parallel graphics, and then the use of communication to allow this parallelism to be exploited.

#### 3.1 Parallelism

There are two broad forms of parallelism to exploit in parallel graphics:

- Task Parallelism performs some or all of the various stages of the graphics pipeline simultaneously.

- **Data Parallelism** duplicates some or all of the stages of the graphics pipeline to process multiple primitives simultaneously.

Task parallelism is the most commonly exploited form of parallelism. Because primitives require varying amounts of work as they progress through the pipeline, exploiting task parallelism requires choosing the ratio of performance between various pipeline stages. One of the choices is the ratio of rasterization to geometry performance. For many modern graphics pipelines the balance is approximately 20:1, in other words there are 20 pixels of

rasterization performance for every 1 vertex of geometry performance. Because the computation per primitive varies throughout the pipeline, and depends on characteristics of the input not known a priori (the primitive size), the operation of pipeline will generally be limited by a single stage, rather than taxing all pipeline stages equally. Moreover, most scenes exhibit a skewed input distribution, with almost all of the primitives much smaller than the balanced primitive size, and a few primitives being very large. The result can be that while the rasterizer processes a large primitive the geometry processor sits idle, waiting for the rasterizer to accept subsequent primitives. The affect can be mitigated by introducing buffering between stages, particularly at those points where work may expand. For example, SGI's InfiniteReality includes a 65,536 vertex FIFO between the geometry processors and the rasterization processors to allow the geometry processors to continue to make forward progress while the rasterization processors are rasterizing a large triangle or triangles [Montrym et al., 1997].

Although task parallelism has challenges of its own, we are primarily concerned with the use of data parallelism. Data parallelism allows the combination of multiple graphics pipelines to achieve higher levels of performance, limited only by the efficiency of the resulting combined system. We can further divide data parallelism into two categories, based on the granularity of parallelism:

- Interframe Parallelism computes multiple frames in parallel.

- Intraframe Parallelism computes a single frame in parallel.

Interframe parallelism increases frame throughput, without decreasing frame latency. For many applications, such as rendering the frames of a movie, it may be acceptable to not address latency. However, interactive computer graphics is generally restricted to operate at human time scales, which limits acceptable latency to a hundred milliseconds or less in many cases. Thus interframe parallel approaches remain limited by the performance of a single pipeline – as soon as the rendering time for the scene on one pipeline exceeds the user's latency tolerance, the system ceases to scale. This generally limits such systems to low degrees of parallelism. Despite its disadvantages, interframe parallelism has the significant advantage of being straightforward to exploit, and in many cases may be readily

| Ι | output image area                  |

|---|------------------------------------|

| T | image parallelism tile size        |

| n | number of pipelines, or processors |

| d | average depth complexity           |

| 0 | average overlap factor             |

**Table 3.1**: Analysis Notation

retrofitted onto an existing graphics system. For example, SGI's SkyWriter system could compute 2 frames in parallel, and was implemented as a small set of extensions to their VGXT architecture [Silicon Graphics, c 1990a, Silicon Graphics, c 1990b].

Intraframe parallelism can both increase frame throughput and decrease frame latency, by computing a single frame in parallel. Thus, doubling both the size of the input and the size of the graphics system will ideally maintain a constant framerate under both interand intra-frame parallelism, but intraframe parallelism may also maintain a constant frame latency. Consequently, the remainder of this thesis will focus on the issues of dealing with intraframe parallelism.

We divide our discussion of intraframe parallelism, referred to hereafter as just parallelism, into two categories:

- Object Parallelism partitions the input across parallel processing elements.

- Image Parallelism partitions the output across parallel processing elements.

Object parallelism divides the rendering work by distributing objects (primitives, fragments, etc.) among the processors of a pipeline stage, typically in a round-robin or work-balanced fashion. Image parallelism divides the rendering work by partitioning responsibility for the output image over the processors of a stage, and then routing work to those functional units whose partition it overlaps. We refer to the notation defined in table 3.1 for our analysis of parallelism and communication in this chapter, as well as analyses in subsequent chapters.

### 3.1.1 Object Parallelism

An object parallel pipeline stage partitions the input work across its processors. This partition may be done in a simple round-robin fashion, in a work-balanced fashion, or in many other ways.

The challenge of an object parallel stage, and in general any form of parallelism, is *load imbalance*. The load imbalance is the ratio of the maximum amount of work performed by any processor in the stage, divided by the average amount of work per processor in that stage. The load balance of an object parallel stage can be completely controlled by the choice of work distribution. There are two obstacles to obtaining a good distribution of work. First, it may be difficult to estimate the amount of time required for a particular computation. Second, if the source of the work is also parallel, it may require the multiple work sources to coordinate their distribution, although if each source individually attempts to balance its distribution, that may be adequate.

In an architecture with ordered semantics, the user-specified order of commands must be tracked as those commands are distributed, so the outputs of the stage may be processed in order by subsequent stages. If the work has been distributed in a round-robin fashion, it may be possible to reorder the output by duplicating the round-robin order. With more complicated distribution schemes the ordering information may have to be explicitly passed through the stage. The maintenance of user-specified order has led many architectures which use object parallelism to introduce a point of serialization after an object parallel stage, in order to enforce the ordered semantics. We will see later that this point of serialization can be expensive, although there are systems which distribute this ordering operation.

# 3.1.2 Image Parallelism

An image parallel stage partitions the output work across its processors. Because the partition is by image coordinates of the work, image parallelism requires that we know, at least conservatively, where each piece of work lies on the screen. Moreover, a piece of parallel work must be routed to all the partitions it overlaps, so, unlike object parallelism, image parallelism can introduce duplicated communication and duplicated computation.

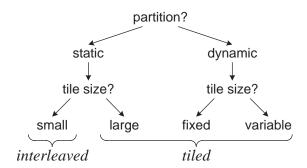

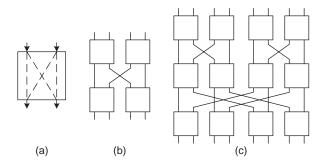

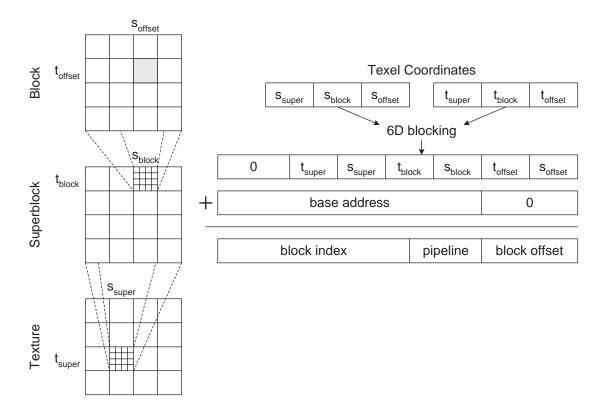

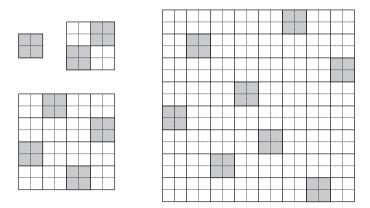

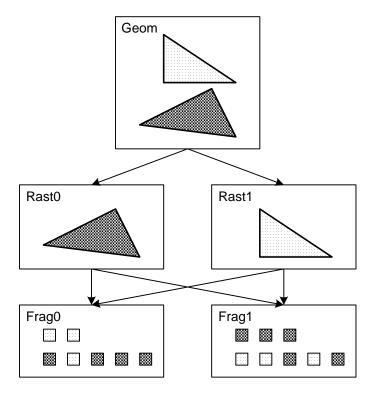

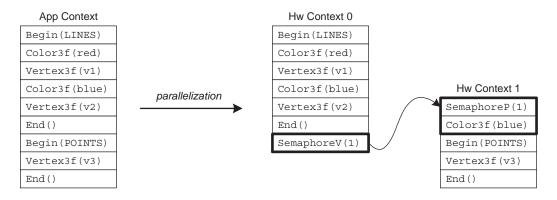

**Figure 3.1**: Image Parallelism Choices. The screen may be partitioned either statically, with a fixed assignment of pixels to processors, or dynamically, with an assignment determined on a per-frame basis, or even dynamically during the course of a frame. When statically partitioned the tiles can either be made small, insuring an excellent load balance at the cost of a higher overlap factor, or large, for a hopefully lower overlap factor, at the cost of a potentially higher load imbalance. When dynamically partitioned the tiles will typically be large, and may even be variably sized, so that the minimum number of tiles can be assigned to each processor while maintaining a good load balance.

The number of partitions that a block of parallel work intersects is the *overlap factor*.

The parallel efficiency of the stage will be determined by the load imbalance of the partitions and the average overlap factor. Both the load imbalance and the overlap factor effectively multiply the input rate seen at a processor, although in slightly different ways. A load imbalance means that each processor gets a different share of the work, and in particular one processor will get more than its fair share of the work. Overlap, which is independent of any load imbalance, means that a given piece of work is processed by more than one processor.

Typically load imbalance is a greater issue for image parallel schemes than object parallel schemes, because the units responsible for a given piece of work are determined solely by that work's screen-space extent. Thus, if the work is not uniformly distributed over the screen, which it generally is not, some partitions will likely have more work than others. This imbalance is exacerbated by temporal effects. The input to a graphics system generally exhibits a large amount of temporal coherence in output space, thus if a piece of work overlaps a partition, subsequent pieces of work are also likely to overlap that partition, which can result in intraframe load imbalances. These effects are typically mitigated

by subdividing the output space into more regions than there are processors, and assigning multiple regions to each processor. In the limit, each tile is only a single pixel, and the load balance can be made nearly ideal. Unfortunately, unless the granularity of work is a single pixel as well, the price of an improved load balance is an increased overlap factor, and a balance must be struck between these two effects. Figure 3.1 describes the choices that can be made when partitioning image parallelism.

A detailed discussion of image tiling schemes is outside of the scope of this thesis. We will confine our discussion to the differences in communication between these approaches, which we broadly classify as *interleaved* and *tiled*. Interleaved parallelism uses a fine interleaving of the screen across the stages, and specifically assumes that the tile size is small enough compared to the average piece of parallel work that each piece of work overlaps all the partitions, and consequently all work is broadcast from the previous stage. Tiled parallelism typically uses a coarser tiling than interleaved parallelism, but specifically differs in that it does not assume that each piece of work overlaps all the partitions, but instead sends the work to only those partitions it overlaps. Chen et al. put forth models of the impact of overlap for tiled rendering, and verify their models experimentally [Chen et al., 1998].

In 1977 Fuchs described an architecture for parallel polygon rasterization which was based on a central unit broadcasting primitive descriptions to a set of processing elements with finely interleaved (1 pixel granularity) responsibility for the screen [Fuchs, 1977]. Fuchs and Johnson went on to more fully describe a system based on this architecture in 1979 [Fuchs and Johnson, 1979]. They stressed the near limitless scalability of this system, in which sets of processing boards and associated memory units could be plugged into a backplane bus which distributes the broadcast polygons as well as the output video signal. Although broadcast buses were de rigueur at the time, it is interesting that they made no mention of the bandwidth of this bus, or the accompanying calculation of the maximum rate at which primitives could be broadcast on the bus, which would obviously limit their performance once adequate rasterization parallelism was provided.

In a 1980 paper Parke describes an architecture for tiled rasterization [Parke, 1980]. Unlike Fuchs's use of broadcast communication, Parke uses a dynamic routing network with "splitter" units that build a tree network. Each splitter recursively divides the screen in half, routing input work appropriately. Although Parke's system only had a single source

of geometry, it was clearly on the path to a scalable switch interconnect. Parke makes a number of trenchant observations, both about the earlier interleaved proposal of Fuchs and about his own architecture.

Referring to Fuchs's architecture, Parke states:

"The broadcast approach suffers from the fact that each processor must deal with every polygon and every edge. This results in performance which approaches a polygon-edge overhead value as additional processors are added rather than approaching zero."

Here Parke has drawn out one of the essential limitations of all schemes which rely on broadcast parallelism. There is a fixed cost to dealing with each piece of work, so increasing parallelism can do no better than this fixed overhead.

Later, referring to his own architecture, Parke says:

"The splitter architecture depends on a uniformly distributed image environment. If the environment is not uniformly distributed, it is possible to saturate a branch of the splitter tree while the other branches are idle. The worst case is when all the image description primitives lie in a single region. For this case only one single image processor will be active, the rest remaining idle."

Parke identifies that the limitation of an approach with coarse-grained parallelism is sensitivity to the image load balance. He describes a hybrid architecture to merge the strengths of an interleaved and a tiled approach to rasterization. This architecture uses his splitter units for the initial stages of communication, but instead of fully expanding the tree so that each tile is the responsibility of a single processor, he truncates the tree and makes each tile the interleaved responsibility of a number of processors. By choosing the depth of this tree the overhead of broadcasting primitives to multiple processors can be balanced against the potential load imbalance of tiling.

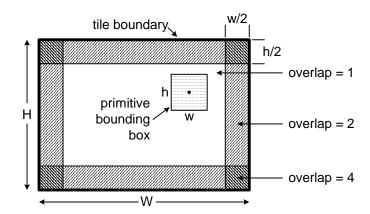

Molnar et al. provide an estimate of the overlap factor O [Molnar et al., 1994]. We define the size of a tile as  $W \times H$ , and the average primitive bounding box as  $w \times h$ , as shown in the figure below, after the figure of Molnar et al.

The center of the primitive can fall anywhere with respect to a tile. In particular, it can fall within a corner, in which case it overlaps this region and the three adjacent regions, with probability

$$\frac{4(w/2)(h/2)}{WH}$$

The primitive may fall along an edge, but not in a corner, in which case it overlaps two regions, with probability

$$\frac{2(w/2)(H-h) + 2(W-w)(h/2)}{WH}$$

Finally, the primitive may lie within the center of the tile, in which case it overlaps just this tile, with probability

$$\frac{(W-w)(H-h)}{WH}$$

The overlap factor O is the expected number of overlapped tiles, which is simply these probabilities weighted by the resulting overlap of a primitive falling in each of these regions.

$$O = \left(\frac{W+w}{W}\right) \left(\frac{H+h}{H}\right)$$

This equation has the expected behavior that when the tile size is much larger than the primitive bounding box  $(W \gg w \text{ and } H \gg h)$  the overlap factor approaches one and when the primitives are large compared to the tile area  $(w \gg W \text{ and } h \gg H)$  the overlap factor approaches the ratio of the primitive area to the tile area. Another useful way to view this

equation is as

$$O = \left(1 + \frac{w}{W}\right) \left(1 + \frac{h}{H}\right)$$

which makes clear that all that is important is the ratio of the primitive edge to the tile edge. If the screen size is doubled, which doubles the primitive size, and the tile size is doubled, then obviously the overlap factor remains unchanged.

# 3.1.3 Object Parallel to Image Parallel Transition

The input to the graphics systems always provides us with object parallelism, as the application is specifying primitives. Similarly, the output of the graphics system always uses image parallelism, because the final output is a stream of pixels to a display device. Between the input and the output of the graphics system we have the flexibility to use object parallelism and image parallelism as we see fit.